Stephen_Usher

Well-known member

A couple of months back I bought a 1MB SRAM card for my Macintosh Portable (non-backlight) from a vendor in France via eBay. Unfortunately the vendor lied that it was in full working order as it didn't work. (Thankfully I got my money refunded and he didn't want it back.)

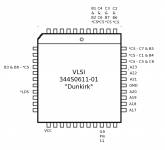

Well, something terrible had happened to the card all the chips connected directly to the address and databuses were fried, including the 74AC24x chips on the board were fried. I'm guessing that the VLSI custom chip is too.

After replacing the 74AC24x chips the card partly works. It mostly doesn't pass the memory test but once in a while I managed to get to the debugger.

After doing this once I tested the memory and it does work to a point. I I can read and write to it fine, but the data is replicated every few kilobytes, so it looks like the chip select isn't working, i.e. the VLSI chip is shot.

So as to get further with the diagnosis I'll either need a schematic of the card or at the very least the pin-out and functionality of the custom VLSI "Dunkirk" chip. Does anyone have either of these?

If in any doubt, I've attached an image of the board (before chip replacement).

Well, something terrible had happened to the card all the chips connected directly to the address and databuses were fried, including the 74AC24x chips on the board were fried. I'm guessing that the VLSI custom chip is too.

After replacing the 74AC24x chips the card partly works. It mostly doesn't pass the memory test but once in a while I managed to get to the debugger.

After doing this once I tested the memory and it does work to a point. I I can read and write to it fine, but the data is replicated every few kilobytes, so it looks like the chip select isn't working, i.e. the VLSI chip is shot.

So as to get further with the diagnosis I'll either need a schematic of the card or at the very least the pin-out and functionality of the custom VLSI "Dunkirk" chip. Does anyone have either of these?

If in any doubt, I've attached an image of the board (before chip replacement).