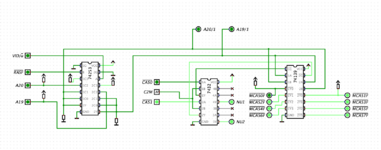

I finally figured out and fixed the sound issue with the 512 cycle refresh mod! As suspected, VA8 and HIGH being swapped between RA0 and RA8 results in some sound data being stored (initiated by the CPU) into a

new location in memory, while the sound hardware for accessing memory is still expecting data at the

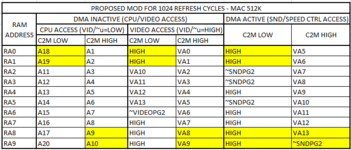

old location. To visualize exactly how the sound hardware accesses memory, I added to the tables I previously made.

View attachment 76179

View attachment 76180

The differences are highlighted. Yellow highlight represents a known difference, and green represents an unknown. The Mac Plus table has gray text for RA9 to indicate that it isn't something the Mac 512K can be compared against.

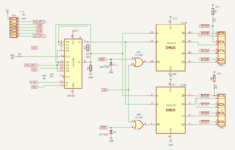

The tables were expanded to include an additional logic input: DMA. The OE pins on the '253s are wired so they are only active when DMA is not occurring, which is anytime sound or floppy drive speed control is

not accessing memory. One caveat is the '253 U13G which has its OE pin tied low, so it is always active. More on that later! The '257s OE pins are connected to active when DMA is occurring. They are the

other source which creates the RA# lines, except they don't create anything for RA8 which is fully controlled by U13G.

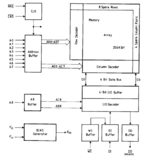

On the Mac Plus, RA8 is created by a '253 and also as an output from BMU2. I don't know exactly what the logic in BMU2 does for RA8, but I took a guess which happened to work out.

For RA0, lifting pin 2 on U2F and tying it high, which follows the thought that swapping VA8 for HIGH when DMA is inactive means that we must also swap VA13 for HIGH when DMA is active, is correct. I suspected the missing part was that we must reintroduce VA13 for RA8 when DMA is active, specifically when C2M is high.

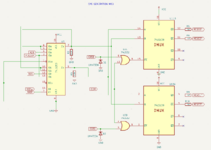

I achieved this by implementing another multiplexor. I used a '253 because it's what I have, but it could have been a '257 like the rest of the sound hardware memory access circuit. I only used half of the IC, so one OE pin was tied high to disable it. The half that I used I connected similar to the Mac's '257s for the sound hardware as follows:

Pin 1 (OEa): ~DMA - only active when sound hardware is accessing memory

Pin 2 (S1): tied LOW - never select A3 or A2

Pin 3 (A3): tied LOW - not used

Pin 4 (A2): tied LOW - not used

Pin 5 (A1): VA13 - selected when C2M is high

Pin 6 (A0): tied HIGH - selected when C2M is low

Pin 6 (ZA): RA8

Other input pins except power: tied low

Other output pin: floating

The remaining issue is that U13G is always in control of RA8, and we must make room for the new multiplexor to take control when sound hardware needs to access memory. I did that the same way the rest of the system's '253s do: by taking the OE pin for the implemented half o the IC (pin 1) and connecting it to the DMA signal.

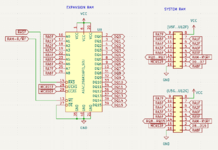

Here's the resulting table for this logic, highlights indicate a change from the stock Mac 512K:

View attachment 76183

View attachment 76184

View attachment 76185

View attachment 76186