I hope I'm not too late to the party on this thread! I've recently been looking into the Color Classic's ROM, in particular the tables used for setting up the MMU, and I think some of the research I've been doing might be relevant to this discussion. The Color Classic (and likely the LC II as well) have a strange physical memory map.

On most 68k Macs, the ROM is

physically at something like 0x40800000. Sometimes on older machines it's even mapped to the entire range of 0x40000000 to 0x50000000. This usually leaves a ton of space starting at 0x0 for RAM. For example, the IIci seems to have everything in the physical address space from 0 to 0x3FFFFFFF (1 GB) reserved for RAM, although I suspect it's really only is capable of decoding 0 to 0x7FFFFFF (128 MB).

On the Color Classic, and I'm assuming also the LC II, the physical memory map is...weird. I think it's because of the way that some of the higher address lines don't get decoded by the Spice chip (or in the case of the LC II, the V8 chip). Since A30 doesn't get fed into the V8/Spice/Eagle, it's not even capable of differentiating between physical addresses 0x40000000 and 0x00000000, so the address map definitely had to change from how other systems like the IIci do it. The MDU in the IIci, in comparison, has access to all 32 address lines, so it doesn't have this silly limitation.

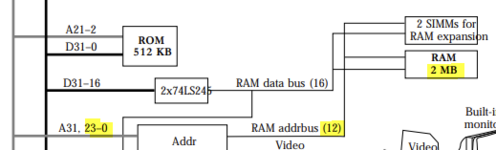

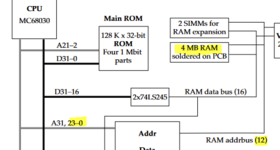

So instead, the CC's ROM is physically mapped from 0xA00000 to 0xDFFFFF, which leaves room for up to 4 MB of ROM. The CC only used 1 MB of ROM, but I think this means there is room for 3 more MB of ROM (can you say bootable 3 MB ROM disk?

) The MMU in 32-bit mode gets set up so that you effectively access it at 0x40A00000, but it's really getting turned into a physical address of 0xA00000 under the hood. BTW, I think this also explains why in 32-bit mode, these models have the ROM at virtual address 0x40A00000 instead of 0x40800000 like most others.

Taking this further, the physical address space reserved for RAM is 0x0 to 0x9FFFFF -- which is 10 MB in size. Exactly matching the limitation we all know well.

I guess my overall question is: doesn't this mean the 10 MB limit has to do with the way that the V8/Spice/Eagle/etc. chipsets decode addresses? It kind of explains, in my mind anyway, why SizeMemory is limiting itself to 10 MB total. If it were possible to have more than 10 MB, where would the additional memory be mapped physically? It can't go directly after the first 10 MB, because that's where the ROM is. Is the V8/Spice capable of mapping that extra 2 MB of RAM somewhere else in the physical address space?

It does make me wonder what the Presto 040 does to allow making full use of the 12 MB. Maybe there's a hardware aspect to it as well? Since the card has access to the full set of A0-A31 address lines on its 040 CPU, maybe it does some special address decoding of its own? Or is it just patching the ROM's MMU tables? I can't figure out in my head how it would work as long as the Spice/V8/etc. chip is still involved, unless those chipsets have some crazy way to remap the extra RAM somewhere else.

The LC III is completely different. The Sonora chipset it uses is more like normal Macs where it's fully decoding the address lines so the ROM is physically mapped at 0x40800000 and there's plenty of room below that for lots of RAM.

Is my understanding here completely off base? I would love to be proven wrong!