I remember Adam Black saying in one of his latest videos that the reason we see a clean black screen with the Sad Mac icon is because the ROM directly controls the display at that point. It bypasses the RAM and writes to the screen itself. When we see the Sad Mac icon over something else , it means at least the Mac is able to write something to the screen using RAM access. So, its better when you see those vertical lines than nothingI also tried the above configuration but with the RA9F generation in place to utilize the entire 2 MB of connected memory. This resulted in a decent looking screen during the power on tests, but it failed to complete them. The screen still has bad pixels here and there which indicate bad or missing bits. The power on tests take much more time which tracks since it’s 4x as much memory.

View attachment 74266

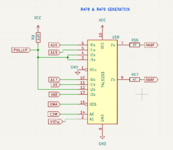

I thought I would look at the RAM-RD signal on the logic board’s memory output buffers compared to the RAM-R/~W signal and a ~CAS signal. Once my oscilloscope probes were connected, I found the power on BONG to be very distorted, and the screen was distorted as well. I narrowed it down to the RAM-R/~W signal which is used by the RAM ICs as a write enable, and my implementation uses it to control the data input buffers. Switching my probe from 1x to 10x helped drastically, but still had a negative effect on the system. It seems that this signal is very much affected by outside influence, even a high impedance one!

I wonder if the delay of my data input buffers being driven by this signal is right on the cusp of being outside acceptable timing tolerance, and perhaps the added capacitance of the long leads, breadboard, and oscilloscope probe is pushing it over the boundary.

I’m not sure what to do with that thought, since I’m pretty certain I need those buffers. Maybe there’s a way to generate a logically equivalent signal which occurs a little sooner? Or maybe the added capacitance is keeping it low longer than it should be, and I should gate it with another signal to ensure that it goes high sooner?

I just hope this particular rabbit hole is fruitful.

Last edited: