Golden Potato

Well-known member

I think you’re exactly right. In the scenario you described when the logic board CAS is low, but the ‘139 output is high, a voltage divider is formed. To simplify, let’s say the system’s CAS output is perfectly 0 V, and let’s also say the high output of the ‘139 does not contribute to the circuit at this time (although it’s not, think of it as an open collector output just to really simplify things).Great news!.

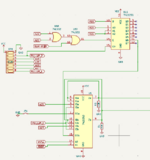

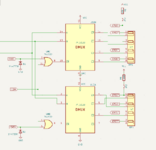

BTW, I'm taking a closer look at those 150 ohm resistors. The MacSnap likely adds to the mainboard memory, so its function might be a kind of trick to override the original signals. Maybe I'm talking gibberish, but as far as I understand, a low value resistor in this configuration is more likely used to prioritize / reinforce the 74LS139's output by weakening any opposing signals rather than acting as a traditional pull-up resistor... Meaning if that 74LS139 goes high (unasserted), an opposite low CAS (asserted) signal coming from the mainboard circuitry will have a difficult time to be "seen". Perhaps both signals will always be in sync, and the purpose of the resistor is to provide enough current for the corresponding lower / upper 8 ICs on the mainboard... It puzzled me why use those resistors only with the CAS signals that go to the mainboard...

You have:

5 V -> 150 ohm -> 47 ohm -> DRAM IC CAS inputs -> logic board CAS resistor (47 ohm) -> 0 V (logic board CAS output low).

47 / (47+47+150) x 5 V = 0.96 V which, if the signal started out low, should theoretically not trigger the DRAM CAS inputs.

It still works for the case when the expansion board tries to drive the logic board’s DRAM CASF signals low since the respective CAS signal on the logic board will also be low as that’s the signal from which the expansion board’s CAS signal is derived. I don’t think it’s possible for the logic board’s CAS signal to be high when the respective CAS signal on the expansion board is low. I hope that wasn’t as confusing as I’m afraid I phrased it!