That was my understanding as well.My understanding is that the data bus (D0 to D31) is directly wired to everything -- ROM, RAM, everything else imaginable. Whatever is being addressed is allowed to put stuff on the bus for the CPU to read.

It's time for me to crack the books and unlimber the continuity tester again.The ROM has chip select/output enable pins to tell it when to output data and it has its own address space. A0 of the ROM socket is not wired directly to A0 of the CPU, but rather through some kind of address decoding logic so that it knows the addresses from $40000000 to $50000000 should be passed on to the ROM SIMM's A0 through A20 or whatever.

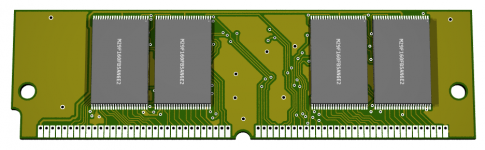

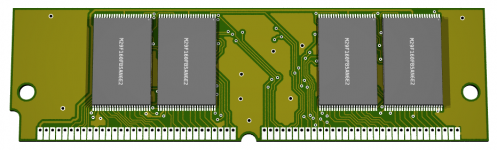

My understanding was that all memory runs through a controller, Paging (whatever that is) is done by the MMU. I'll need to check on that out. More is accessible through the RAM interface than meets the eye. Video Out solutions for the PB100 were wedged into the system through its RAM expansion slot as one example.I think RAM behaves slightly differently in regard to where you tell it what to read/write (I've never really looked that up and I should), but it's still the same idea -- I'm fairly sure the RAM socket only has the RAM space wired up. Otherwise, how would each RAM chip know that it's supposed to listen to the section of the machine's address space reserved for RAM as opposed to the address space reserved for ROM or the sound chip or whatever else?

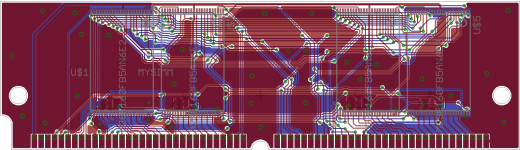

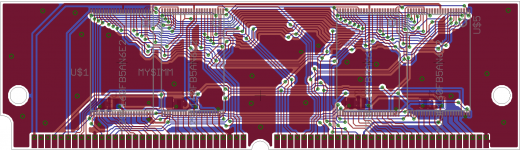

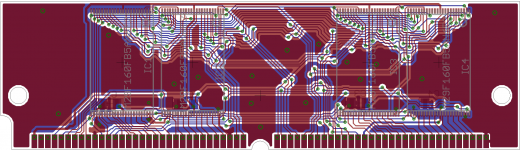

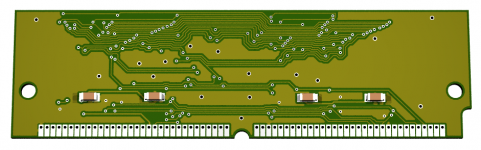

The pics in my head show all the Data and Addressing lines hooked up to the 72 pin SIMM, the differences being the Row Address Select and Bank select lines, IIRC. 32 bits of address space is 32 bits of address space AFAIK. As you said, how that's chopped up via the decoding circuitry is a different story . . .Anyway, I haven't researched it much, this is just what I'm thinking off the top of my head. It's very possible I'm forgetting something, but that's just how I'm seeing it in my head...

. . . but that's where the patch wiring I mentioned enters the picture! }