How does the Nubus bridge tell the Mac there's a declrom somewhere? That goes against my understanding of how this all works, so if you've got something specific in mind, I'm all about increasing my understanding...

Here's my understanding of the process from connector to System software:

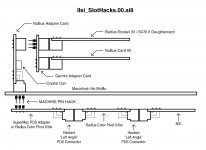

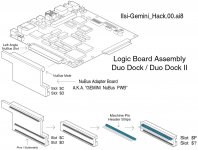

The /NMRQ pin of the Nubus connector on the Nubus bridge adapter goes to /IRQ1 of the 030 PDS connector, and the ID0-3 pins of the Nubus connector indicate to the card to use slot 9. In the IIx, each slot's /NMRQ line goes to VIA2 register A bits 0-5 (one per, slot 9's /NMRQ goes to bit 0, slot A goes to bit 1, etc.). Bits 0-5 of VIA2's register A are then ORed by VIA2 (or RBV, in the IIsi/IIci case) into /SLOTIRQ, which is the actual processor interrupt. The bridge adapter only supports 1 card at slot 9, so /NMRQ goes to /IRQ1. When /SLOTIRQ indicates an interrupt, the CPU interrupts, the SlotMgr's interrupt handler fires, the SlotMgr then checks VIA2 register A to see which (one or more) slots interrupted, and fires off the appropriate interrupt handlers.

So... A (pseudo)slot can interrupt the CPU by toggling /SLOTIRQ, but unless the appropriate bit gets set in that VIA2 register, no one knows what interrupted, and that slot's interrupt handler (if any) won't get run. There's no way an 030 PDS card can inform SlotMgr to go look at some other bit to determine which slot interrupted.

Now, this is all pretty machine specific, since AFAIK, later models have a different way of checking which slot interrupted. As it stands, the IIsi/IIci are already kind of different from the II/IIx/SE/30 since the RBV emulates this VIA2 register and the II/IIx/SE/30 have an actual 2nd VIA.

This gets me thinking whether the Nubus bridge could support additional Nubus cards if ID0-3 were set appropriately, and the additional slots' /NMRQ line went to the corresponding /IRQ line of the 030 PDS.

But again, that's just my understanding, so if there's something specific I should be looking at, let me know...

As for the Rocket, I don't think anything changes. The above is how the system works, and the Rocket has to work within the confines of the existing system. A master in Nubus terminology simply means whoever is initiating the addressing at the current time. Multiple cards can be masters on Nubus, just not during the same cycle. The CPU is always capable of acting as a master, as are Rockets, some SCSI cards, etc.