zigzagjoe

Well-known member

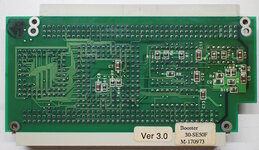

Got my hands on one of these and reverse engineered it. GAL JEDEC files attached.

Vital stats: 47 MHZ CPU (x3 SYSCLK), optional 47 MHZ FPU, no additional cache.

Around 2x performance in most benchmarks. Recommend to use with System 6 - 7.1 with stock SE/30 ROMs.

Compatibility: Incompatible with Micron Xceed, possibly Shiva Etherport SE30.

Tested working with Interware GrandVimage, Asante Maccon, Farallon TP594

With accelerators in the SE/30, there are a few-timing sensitive components that will not function correctly unless compensated for. Sound and Floppy access are high on that list. Higher end 68030 accelerators (Diimo, PowerCache) recognize these addresses in hardware and slow things down there; low end accelerators such as the Dove Marathon and Sonnet Allegro rely on software fixes instead (and usually can't boot from floppy).

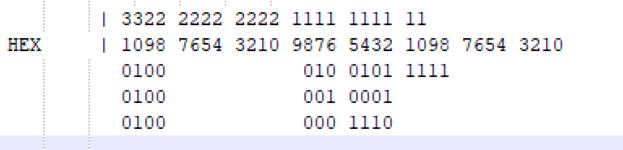

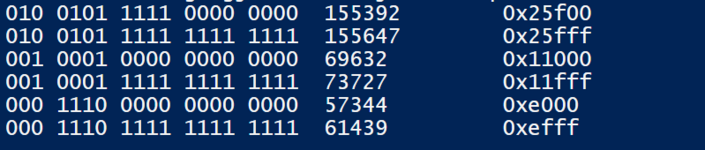

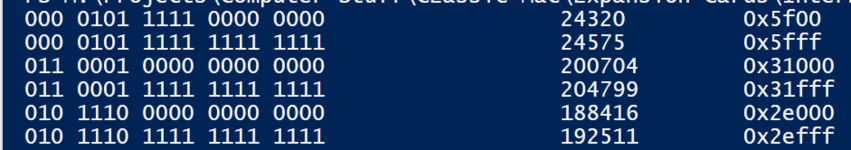

The Booster recognizes these accesses in hardware, like the Diimo and Powercache. The specific mechanism it uses to slow the CPU is interesting: rather than slow the CPU clock, or insert wait states directly, they choose to inhibit the CPU's cache for 3 specific ROM ranges. This means the CPU is forced to (more or less) read and execute at the speed of the system bus / ROM as it needs to fetch each instruction, with a net result of keeping timing in check for those sensitive routines.

Why is this important? Well, it isn't, unless you run a ROM other than the original SE/30 ROM (or a modified version thereof) as these offsets would then differ. Predictably, floppy booting ceases to work if using an IIsi ROM. It would be possible to add a jumper to allow selecting between SE/30 and an IIsi-based ROM, but of course, need to ID these routines first and the corresponding ones in the IIsi ROM. One of these ranges I believe I localized to the Sony floppy driver, but I didn't have as much luck with the others.

This is also a problem when running newer versions of Mac OS: System 7.5x seems to patch or replace the sound driver, which then starts has minor sound glitches. So this is where a recommended max of 7.1 comes from, though otherwise 7.5x seems to function fine.

Speculation: As IIx and IIcx use the same ROM, clock speeds, GLUE ASIC, etc - I have a feeling they'll also work with this design. Will be testing this.

Card compatibility: This card does not support any PDS card that requires the STERM (Synchronous Termination) signal. Notably, this includes the Micron Xceed cards. Interware appears to have originally designed for this functionality, but I've found that the GAL connection that would have gone to it is factory cut on mine and in all other images I've seen. Likewise, the GAL equations that would have been responsible has been removed. As this is a hardware limitation, this wouldn't be easily fixed.

I've also found that if a Shiva Etherport SE30 is installed, it will hard lock when booting at the Welcome to Macintosh screen. This may be resolvable in software - this is something different from the STERM issue.

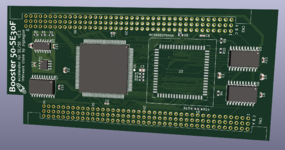

Sneak peak.... Clones will be available before too long.

Vital stats: 47 MHZ CPU (x3 SYSCLK), optional 47 MHZ FPU, no additional cache.

Around 2x performance in most benchmarks. Recommend to use with System 6 - 7.1 with stock SE/30 ROMs.

Compatibility: Incompatible with Micron Xceed, possibly Shiva Etherport SE30.

Tested working with Interware GrandVimage, Asante Maccon, Farallon TP594

With accelerators in the SE/30, there are a few-timing sensitive components that will not function correctly unless compensated for. Sound and Floppy access are high on that list. Higher end 68030 accelerators (Diimo, PowerCache) recognize these addresses in hardware and slow things down there; low end accelerators such as the Dove Marathon and Sonnet Allegro rely on software fixes instead (and usually can't boot from floppy).

The Booster recognizes these accesses in hardware, like the Diimo and Powercache. The specific mechanism it uses to slow the CPU is interesting: rather than slow the CPU clock, or insert wait states directly, they choose to inhibit the CPU's cache for 3 specific ROM ranges. This means the CPU is forced to (more or less) read and execute at the speed of the system bus / ROM as it needs to fetch each instruction, with a net result of keeping timing in check for those sensitive routines.

Code:

0xE000 - 0xEFFF

0x11000 - 0x11FFF

0x25F00 - 0x25FFFWhy is this important? Well, it isn't, unless you run a ROM other than the original SE/30 ROM (or a modified version thereof) as these offsets would then differ. Predictably, floppy booting ceases to work if using an IIsi ROM. It would be possible to add a jumper to allow selecting between SE/30 and an IIsi-based ROM, but of course, need to ID these routines first and the corresponding ones in the IIsi ROM. One of these ranges I believe I localized to the Sony floppy driver, but I didn't have as much luck with the others.

This is also a problem when running newer versions of Mac OS: System 7.5x seems to patch or replace the sound driver, which then starts has minor sound glitches. So this is where a recommended max of 7.1 comes from, though otherwise 7.5x seems to function fine.

Speculation: As IIx and IIcx use the same ROM, clock speeds, GLUE ASIC, etc - I have a feeling they'll also work with this design. Will be testing this.

Card compatibility: This card does not support any PDS card that requires the STERM (Synchronous Termination) signal. Notably, this includes the Micron Xceed cards. Interware appears to have originally designed for this functionality, but I've found that the GAL connection that would have gone to it is factory cut on mine and in all other images I've seen. Likewise, the GAL equations that would have been responsible has been removed. As this is a hardware limitation, this wouldn't be easily fixed.

I've also found that if a Shiva Etherport SE30 is installed, it will hard lock when booting at the Welcome to Macintosh screen. This may be resolvable in software - this is something different from the STERM issue.

Sneak peak.... Clones will be available before too long.

Attachments

Last edited: