Trash80toHP_Mini

NIGHT STALKER

@max1zzz thanks so much for the layers of your IIcx Redux.

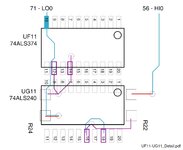

I've reconstructed the traces/chips/pads for the three signals that meander down off NUCHIP in the NuBus section of the Bomarc Schematic.

Trying to figure out where ARST, LO0 and HI0 go and what they are doing?

Some of the circuit seems like it can be recreated on the NuBus Adapter side of the PDS?

Red = Solder Side Traces

Blue = Component Side Traces

Strange:

Strange:

HI0 and LO0 are jumbled into multiple pins on one side or the other of resistors on the solder side?

ARST is connected to a pair of pins on a resistor pack?

How much deeper do you think I need to dive into this?

Next step would seem to be scouring the remainder of the pages for the ICs to see what might be up?

I've reconstructed the traces/chips/pads for the three signals that meander down off NUCHIP in the NuBus section of the Bomarc Schematic.

Trying to figure out where ARST, LO0 and HI0 go and what they are doing?

Some of the circuit seems like it can be recreated on the NuBus Adapter side of the PDS?

Red = Solder Side Traces

Blue = Component Side Traces

Strange:

Strange:HI0 and LO0 are jumbled into multiple pins on one side or the other of resistors on the solder side?

ARST is connected to a pair of pins on a resistor pack?

How much deeper do you think I need to dive into this?

Next step would seem to be scouring the remainder of the pages for the ICs to see what might be up?