Trash80toHP_Mini

NIGHT STALKER

Back to basics: forever project reboot.

68kmla.org

68kmla.org

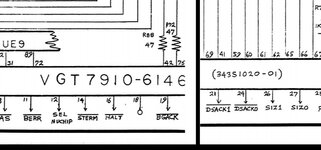

New approach is to take the IIsi NuBus Adapter on a trip back in time. It now seems to me that it's likely that NuChip30 may be the problem.

Nuchip ASIC replaced the discrete component implementation in the early release Macintosh II, supporting 16MHz clock of the series

NuChip 30 ASIC development required for support of the faster 25MHz IIci and 20MHz IIsi clocks in that generation of series.

____ NuChip 33 developed for support of later machines.

Hardware/firmware backward compatibility with earlier, slower NuBus machines would be unnecessary.

Given:

Macintosh SE/30 was a reduced form factor, PDS substitution (upgrade?) of the IIcx NuBus (NuChip) architecture.

Theory:

NuBus implementation of IIci/IIcx generation burned bridge of hardware/firmware implementation in earlier machines?

WAG:

Replacement of NuChip 30 controller on the IIsi NuBus adapter with NuChip from II/IIx/IIcx is worth a shot?

Such may rebuild the burned NuBus bridge to SE/30?

Assumption:

NuBus controllers would be agnostic in terms of transceiver implementation support?

Thoughts?

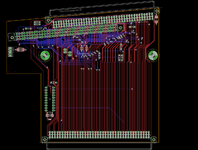

Project30 - fourth edition - Radius IIsi NuBus Adapter build for SE/30?

Five years and two days to the date, Project30 is back on the bench thanks to new developments. Replace the IIsi NuBus Adapter in this pic from back then . . . . . . with this card we found at the time . . . . . . add the 40MHz clock from the former to the Radius adapter and...

68kmla.org

68kmla.org

New approach is to take the IIsi NuBus Adapter on a trip back in time. It now seems to me that it's likely that NuChip30 may be the problem.

Nuchip ASIC replaced the discrete component implementation in the early release Macintosh II, supporting 16MHz clock of the series

NuChip 30 ASIC development required for support of the faster 25MHz IIci and 20MHz IIsi clocks in that generation of series.

____ NuChip 33 developed for support of later machines.

Hardware/firmware backward compatibility with earlier, slower NuBus machines would be unnecessary.

Given:

Macintosh SE/30 was a reduced form factor, PDS substitution (upgrade?) of the IIcx NuBus (NuChip) architecture.

Theory:

NuBus implementation of IIci/IIcx generation burned bridge of hardware/firmware implementation in earlier machines?

WAG:

Replacement of NuChip 30 controller on the IIsi NuBus adapter with NuChip from II/IIx/IIcx is worth a shot?

Such may rebuild the burned NuBus bridge to SE/30?

Assumption:

NuBus controllers would be agnostic in terms of transceiver implementation support?

Thoughts?

Last edited: