You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

PowerBook 100 Accelerator Insanity

- Thread starter Trash80toHP_Mini

- Start date

Trash80toHP_Mini

NIGHT STALKER

Given success of my 68000 socket testing, I've been thinking along the lines of cloning the Perfomer as a SE and Plus Accelerator. Successfully building a prototype with socketed DIP GALs would be the obvious second step in developing a mini-sized version for the PowerBook 100. It's also a pretty neat thing to attempt on its own. [ ]

]

So I'm looking to trade something from the hoard for a second Performer with socketed CPU. I need another one to depopulate/trace out in order to clone/adapt MicroMac's PCB on a 10cm x 10cm SEEED board.

Fourth step in the current PB100 insanity would be to adapt that to the run directly off the pads on the top deck of the 100's daughtercard. Successfully testing my Performer on those pads with the socket adapter kluge outlined above is the third stage.

Adding RAM to the Performer for Compact Virtual playtime on Plus/SE would be the precursor to doing same for the PB100.

Crossing fingers that this insanity will also lead to something I can install in my Luggable. h34r:

h34r:

So I'm looking to trade something from the hoard for a second Performer with socketed CPU. I need another one to depopulate/trace out in order to clone/adapt MicroMac's PCB on a 10cm x 10cm SEEED board.

Fourth step in the current PB100 insanity would be to adapt that to the run directly off the pads on the top deck of the 100's daughtercard. Successfully testing my Performer on those pads with the socket adapter kluge outlined above is the third stage.

Adding RAM to the Performer for Compact Virtual playtime on Plus/SE would be the precursor to doing same for the PB100.

Crossing fingers that this insanity will also lead to something I can install in my Luggable.

Trash80toHP_Mini

NIGHT STALKER

PowerBook 100 DevNote

PowerBook 100 Specifications

PowerBook 100 ServiceSource

PowerBook 100 User Guide

MicroMac Performer

PSRAM JEDEC

PSRAM memory controller

FPGAs/CPLDs

Macintosh Portable ServiceSource

Macintosh SE ServiceSource

PowerBook 100 Specifications

PowerBook 100 ServiceSource

PowerBook 100 User Guide

MicroMac Performer

PSRAM JEDEC

PSRAM memory controller

FPGAs/CPLDs

Macintosh Portable ServiceSource

Macintosh SE ServiceSource

Trash80toHP_Mini

NIGHT STALKER

ROM interface

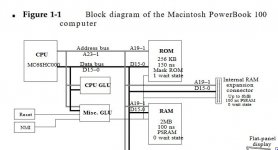

The Macintosh PowerBook 100 uses the same ROM as the Macintosh

Portable. The Macintosh PowerBook 100 is shipped with 256 KB of

ROM permanently soldered to the main logic board. The Macintosh

PowerBook 100 will accommodate a maximum of 4 MB of ROM on

the main logic board, but it does not include a provision for internal

or external ROM expansion. The ROM is arranged as a 128K x 16-bit

array consisting physically of two 28-pin 128K x 8-bit devices with an

access and cycle time of 150 ns.

Sounds to me like the PB100's CPU/RAM/ROM daughtercard should be able to address a full 4MB of ROM if it's built into the accelerator. No provision for internal (on the processor daughtercard) or external (ROM expansion slot) ROM expansion doesn't mean it can't be done, only that it's not supported in hardware. Since the Portable's ROM is used, seems to me like 4MB on the daughtercard can be addressed if it can be made to fit.

Buzzing connections is going rather well, a bit confusing, but well nonetheless. [

Last edited by a moderator:

Trash80toHP_Mini

NIGHT STALKER

RAM expansion connector signals

1___GND___Ground

2___GND___Ground

3___A19___Address bit 19 (buffered)

4___A16___Address bit 16 (buffered)

5___A17___Address bit 17 (buffered)

6___A18___Address bit 18 (buffered)

7___A15___Address bit 15 (buffered)

8___/LW___Lower byte write strobe

9___A13___Address bit 13 (buffered)

10___/LW___Lower byte write strobe

11____A8___Address bit 8 (buffered)

12___A14___Address bit 14 (buffered)

13____A7___Address bit 7 (buffered)

14____A9___Address bit 9 (buffered)

15____A6___Address bit 6 (buffered)

16___A10___Address bit 10 (buffered)

17____A5___Address bit 5 (buffered)

18___A12___Address bit 12 (buffered)

19____A4___Address bit 4 (buffered)

20___/OE.RFSH___RAM output enable and refresh

21____A3___Address bit 3 (buffered)

22___A11___Address bit 11 (buffered)

23____A2___Address bit 2 (buffered)

24___/EXP.CS0___Chip select bit 0

25____A1___Address bit 1 (buffered)

26____D7___Data bit 7 (buffered) to and from main logic board

27____D0___Data bit 0 (buffered) to and from main logic board

28____D6___Data bit 6 (buffered) to and from main logic board

29____D1___Data bit 1 (buffered) to and from main logic board

30____D5___Data bit 5 (buffered) to and from main logic board

31____D2___Data bit 2 (buffered) to and from main logic board

32____D4___Data bit 4 (buffered) to and from main logic board

33____GND___Ground

34___/EXP.CS1___Chip select bit 1

35____D4___Data bit 4 (buffered) to and from main logic board

36____D3___Data bit 3 (buffered) to and from main logic board

37____D2___Data bit 2 (buffered) to and from main logic board

38____D3___Data bit 3 (buffered) to and from main logic board

39____D0___Data bit 0 (buffered) to and from main logic board

40____D1___Data bit 1 (buffered) to and from main logic board

41____D7___Data bit 7 (buffered) to and from main logic board

42____D6___Data bit 6 (buffered) to and from main logic board

43___+5V___+5V RAM power

44____D5___Data bit 5 (buffered) to and from main logic board

45___/EXP.CS5___Chip select bit 5

46___+5V___+5V RAM power

47___/UW___Upper byte write strobe

48___/UW___Upper byte write strobe

49____nc___No connection

50___/EXP.CS2___Chip select bit 2

51___/EXP.CS4___Chip select bit 4

52_____nc___No connection

53___D11___Data bit 11 (buffered) to and from main logic board

54___D12___Data bit 12 (buffered) to and from main logic board

55___D14___Data bit 14 (buffered) to and from main logic board

56___D13___Data bit 13 (buffered) to and from main logic board

57____D8___Data bit 8 (buffered) to and from main logic board

58___D14___Data bit 14 (buffered) to and from main logic board

59____D9___Data bit 9 (buffered) to and from main logic board

60___D15___Data bit 15 (buffered) to and from main logic board

61___D10___Data bit 10 (buffered) to and from main logic board

62___D15___Data bit 15 (buffered) to and from main logic board

63___ D13___Data bit 13 (buffered) to and from main logic board

64____D8___Data bit 8 (buffered) to and from main logic board

65___D12____Data bit 12 (buffered) to and from mainlogic board

66____D9___Data bit 9 (buffered) to and from main logic board

67___D11___Data bit 11 (buffered) to and from main logic board

68___D10___Data bit 10 (buffered) to and from main logic board

69___GND___Ground

70___/EXP.CS3___Chip select bit 3

1___GND___Ground

2___GND___Ground

3___A19___Address bit 19 (buffered)

4___A16___Address bit 16 (buffered)

5___A17___Address bit 17 (buffered)

6___A18___Address bit 18 (buffered)

7___A15___Address bit 15 (buffered)

8___/LW___Lower byte write strobe

9___A13___Address bit 13 (buffered)

10___/LW___Lower byte write strobe

11____A8___Address bit 8 (buffered)

12___A14___Address bit 14 (buffered)

13____A7___Address bit 7 (buffered)

14____A9___Address bit 9 (buffered)

15____A6___Address bit 6 (buffered)

16___A10___Address bit 10 (buffered)

17____A5___Address bit 5 (buffered)

18___A12___Address bit 12 (buffered)

19____A4___Address bit 4 (buffered)

20___/OE.RFSH___RAM output enable and refresh

21____A3___Address bit 3 (buffered)

22___A11___Address bit 11 (buffered)

23____A2___Address bit 2 (buffered)

24___/EXP.CS0___Chip select bit 0

25____A1___Address bit 1 (buffered)

26____D7___Data bit 7 (buffered) to and from main logic board

27____D0___Data bit 0 (buffered) to and from main logic board

28____D6___Data bit 6 (buffered) to and from main logic board

29____D1___Data bit 1 (buffered) to and from main logic board

30____D5___Data bit 5 (buffered) to and from main logic board

31____D2___Data bit 2 (buffered) to and from main logic board

32____D4___Data bit 4 (buffered) to and from main logic board

33____GND___Ground

34___/EXP.CS1___Chip select bit 1

35____D4___Data bit 4 (buffered) to and from main logic board

36____D3___Data bit 3 (buffered) to and from main logic board

37____D2___Data bit 2 (buffered) to and from main logic board

38____D3___Data bit 3 (buffered) to and from main logic board

39____D0___Data bit 0 (buffered) to and from main logic board

40____D1___Data bit 1 (buffered) to and from main logic board

41____D7___Data bit 7 (buffered) to and from main logic board

42____D6___Data bit 6 (buffered) to and from main logic board

43___+5V___+5V RAM power

44____D5___Data bit 5 (buffered) to and from main logic board

45___/EXP.CS5___Chip select bit 5

46___+5V___+5V RAM power

47___/UW___Upper byte write strobe

48___/UW___Upper byte write strobe

49____nc___No connection

50___/EXP.CS2___Chip select bit 2

51___/EXP.CS4___Chip select bit 4

52_____nc___No connection

53___D11___Data bit 11 (buffered) to and from main logic board

54___D12___Data bit 12 (buffered) to and from main logic board

55___D14___Data bit 14 (buffered) to and from main logic board

56___D13___Data bit 13 (buffered) to and from main logic board

57____D8___Data bit 8 (buffered) to and from main logic board

58___D14___Data bit 14 (buffered) to and from main logic board

59____D9___Data bit 9 (buffered) to and from main logic board

60___D15___Data bit 15 (buffered) to and from main logic board

61___D10___Data bit 10 (buffered) to and from main logic board

62___D15___Data bit 15 (buffered) to and from main logic board

63___ D13___Data bit 13 (buffered) to and from main logic board

64____D8___Data bit 8 (buffered) to and from main logic board

65___D12____Data bit 12 (buffered) to and from mainlogic board

66____D9___Data bit 9 (buffered) to and from main logic board

67___D11___Data bit 11 (buffered) to and from main logic board

68___D10___Data bit 10 (buffered) to and from main logic board

69___GND___Ground

70___/EXP.CS3___Chip select bit 3

techknight

Well-known member

I love this thread.But....

1. I am more of a portable guy.

2. I wish I had a PB100, but finding one in decent condition with a decent LCD is way out of my budget so...

I will follow and help where I can, but thats limited.

1. I am more of a portable guy.

2. I wish I had a PB100, but finding one in decent condition with a decent LCD is way out of my budget so...

I will follow and help where I can, but thats limited.

Trash80toHP_Mini

NIGHT STALKER

There's some very strange things going on in that RAM expansion connector pinout. Lots of duplicate data and address signals, what the heck is that all about?

Gotta rearrange that pinout into groups by function.

Gotta rearrange that pinout into groups by function.

Last edited by a moderator:

Trash80toHP_Mini

NIGHT STALKER

THX, I'm having a blast! [I love this thread.But....

1. I am more of a portable guy.

2. I wish I had a PB100, but finding one in decent condition with a decent LCD is way out of my budget so...

I will follow and help where I can, but thats limited.

Have you got anything worked out on what the Portable uses for a memory controller or how it's set up outside of the slot docs? I can't find any info on a schematic for either Luggable or PowerBook 100 anywhere? Even the SE setup ought to be helpful, but so far I've got bopkes.

Outside of brute forcing the GALs, the easiest part of the project will be reverse engineering the Performer. That'd make a nice standalone hack in itself. And then to start building upon that foundation. Gotta track down another Performer to lobotomize.

Last edited by a moderator:

Trash80toHP_Mini

NIGHT STALKER

PB100-RAM Connector Pinout-Grouped

25____A1___Address bit 1 (buffered)

23____A2___Address bit 2 (buffered)

21____A3___Address bit 3 (buffered)

19____A4___Address bit 4 (buffered)

17____A5___Address bit 5 (buffered)

15____A6___Address bit 6 (buffered)

13____A7___Address bit 7 (buffered)

11____A8___Address bit 8 (buffered)

14____A9___Address bit 9 (buffered)

16___A10___Address bit 10 (buffered)

22___A11___Address bit 11 (buffered)

18___A12___Address bit 12 (buffered)

9___A13___Address bit 13 (buffered)

12___A14___Address bit 14 (buffered)

7___A15___Address bit 15 (buffered)

4___A16___Address bit 16 (buffered)

5___A17___Address bit 17 (buffered)

6___A18___Address bit 18 (buffered)

3___A19___Address bit 19 (buffered)

8___/LW___Lower byte write strobe

10___/LW___Lower byte write strobe

47___/UW___Upper byte write strobe

48___/UW___Upper byte write strobe

20___/OE.RFSH___RAM output enable and refresh

24___/EXP.CS0___Chip select bit 0

34___/EXP.CS1___Chip select bit 1

50___/EXP.CS2___Chip select bit 2

70___/EXP.CS3___Chip select bit 3

51___/EXP.CS4___Chip select bit 4

45___/EXP.CS5___Chip select bit 5

27____D0___Data bit 0 (buffered) to and from main logic board

39____D0___Data bit 0 (buffered) to and from main logic board

29____D1___Data bit 1 (buffered) to and from main logic board

40____D1___Data bit 1 (buffered) to and from main logic board

37____D2___Data bit 2 (buffered) to and from main logic board

31____D2___Data bit 2 (buffered) to and from main logic board

38____D3___Data bit 3 (buffered) to and from main logic board

36____D3___Data bit 3 (buffered) to and from main logic board

32____D4___Data bit 4 (buffered) to and from main logic board

35____D4___Data bit 4 (buffered) to and from main logic board

30____D5___Data bit 5 (buffered) to and from main logic board

44____D5___Data bit 5 (buffered) to and from main logic board

28____D6___Data bit 6 (buffered) to and from main logic board

42____D6___Data bit 6 (buffered) to and from main logic board

26____D7___Data bit 7 (buffered) to and from main logic board

41____D7___Data bit 7 (buffered) to and from main logic board

57____D8___Data bit 8 (buffered) to and from main logic board

64____D8___Data bit 8 (buffered) to and from main logic board

59____D9___Data bit 9 (buffered) to and from main logic board

66____D9___Data bit 9 (buffered) to and from main logic board

61___D10___Data bit 10 (buffered) to and from main logic board

68___D10___Data bit 10 (buffered) to and from main logic board

53___D11___Data bit 11 (buffered) to and from main logic board

67___D11___Data bit 11 (buffered) to and from main logic board

54___D12___Data bit 12 (buffered) to and from main logic board

65___D12___Data bit 12 (buffered) to and from main logic board

56___D13___Data bit 13 (buffered) to and from main logic board

63___D13___Data bit 13 (buffered) to and from main logic board

55___D14___Data bit 14 (buffered) to and from main logic board

58___D14___Data bit 14 (buffered) to and from main logic board

60___D15___Data bit 15 (buffered) to and from main logic board

62___D15___Data bit 15 (buffered) to and from main logic board

1___GND___Ground

2___GND___Ground

69___GND___Ground

33___GND___Ground

49___nc___No connection

52___nc___No connection

43___+5V___+5V RAM power

46___+5V___+5V RAM power

I guess the address lines only need to be buffered one way, but the data needs bi-directional buffering. That makes sense, it'll be interesting to look into why there appear to be two data buses. WAG at this point would be that 4MB on the expansion card has its own bus and that the other 2MB share their data bus with the 2MB on the main logic board.

I like that, "main logic board" sounds a lot better and has a more specific meaning than "daughterboard." The other is now the "RAM board" for the same reason. "Memory expansion card" leaves a lot to be desired.

25____A1___Address bit 1 (buffered)

23____A2___Address bit 2 (buffered)

21____A3___Address bit 3 (buffered)

19____A4___Address bit 4 (buffered)

17____A5___Address bit 5 (buffered)

15____A6___Address bit 6 (buffered)

13____A7___Address bit 7 (buffered)

11____A8___Address bit 8 (buffered)

14____A9___Address bit 9 (buffered)

16___A10___Address bit 10 (buffered)

22___A11___Address bit 11 (buffered)

18___A12___Address bit 12 (buffered)

9___A13___Address bit 13 (buffered)

12___A14___Address bit 14 (buffered)

7___A15___Address bit 15 (buffered)

4___A16___Address bit 16 (buffered)

5___A17___Address bit 17 (buffered)

6___A18___Address bit 18 (buffered)

3___A19___Address bit 19 (buffered)

8___/LW___Lower byte write strobe

10___/LW___Lower byte write strobe

47___/UW___Upper byte write strobe

48___/UW___Upper byte write strobe

20___/OE.RFSH___RAM output enable and refresh

24___/EXP.CS0___Chip select bit 0

34___/EXP.CS1___Chip select bit 1

50___/EXP.CS2___Chip select bit 2

70___/EXP.CS3___Chip select bit 3

51___/EXP.CS4___Chip select bit 4

45___/EXP.CS5___Chip select bit 5

27____D0___Data bit 0 (buffered) to and from main logic board

39____D0___Data bit 0 (buffered) to and from main logic board

29____D1___Data bit 1 (buffered) to and from main logic board

40____D1___Data bit 1 (buffered) to and from main logic board

37____D2___Data bit 2 (buffered) to and from main logic board

31____D2___Data bit 2 (buffered) to and from main logic board

38____D3___Data bit 3 (buffered) to and from main logic board

36____D3___Data bit 3 (buffered) to and from main logic board

32____D4___Data bit 4 (buffered) to and from main logic board

35____D4___Data bit 4 (buffered) to and from main logic board

30____D5___Data bit 5 (buffered) to and from main logic board

44____D5___Data bit 5 (buffered) to and from main logic board

28____D6___Data bit 6 (buffered) to and from main logic board

42____D6___Data bit 6 (buffered) to and from main logic board

26____D7___Data bit 7 (buffered) to and from main logic board

41____D7___Data bit 7 (buffered) to and from main logic board

57____D8___Data bit 8 (buffered) to and from main logic board

64____D8___Data bit 8 (buffered) to and from main logic board

59____D9___Data bit 9 (buffered) to and from main logic board

66____D9___Data bit 9 (buffered) to and from main logic board

61___D10___Data bit 10 (buffered) to and from main logic board

68___D10___Data bit 10 (buffered) to and from main logic board

53___D11___Data bit 11 (buffered) to and from main logic board

67___D11___Data bit 11 (buffered) to and from main logic board

54___D12___Data bit 12 (buffered) to and from main logic board

65___D12___Data bit 12 (buffered) to and from main logic board

56___D13___Data bit 13 (buffered) to and from main logic board

63___D13___Data bit 13 (buffered) to and from main logic board

55___D14___Data bit 14 (buffered) to and from main logic board

58___D14___Data bit 14 (buffered) to and from main logic board

60___D15___Data bit 15 (buffered) to and from main logic board

62___D15___Data bit 15 (buffered) to and from main logic board

1___GND___Ground

2___GND___Ground

69___GND___Ground

33___GND___Ground

49___nc___No connection

52___nc___No connection

43___+5V___+5V RAM power

46___+5V___+5V RAM power

I guess the address lines only need to be buffered one way, but the data needs bi-directional buffering. That makes sense, it'll be interesting to look into why there appear to be two data buses. WAG at this point would be that 4MB on the expansion card has its own bus and that the other 2MB share their data bus with the 2MB on the main logic board.

I like that, "main logic board" sounds a lot better and has a more specific meaning than "daughterboard." The other is now the "RAM board" for the same reason. "Memory expansion card" leaves a lot to be desired.

Last edited by a moderator:

Trash80toHP_Mini

NIGHT STALKER

HRMMM?

This is gonna take some thinking about. Anybody got a handle on this paragraph? Sounds a bit like the 16 doubled up data lines are a 32bit bus if looked at in terms of a 68030 board and they would be high and low 16bit chunks to the 68HC000 of the PB100?

Chapter 1 Macintosh PowerBook 100 Hardware

Note:

If you design your RAM expansion card correctly, it will also work in future Macintosh-family, 68030-based portable computers. A 68030-based machine has a 32-bit data bus, whereas the 68HC000 in the Macintosh PowerBook 100 has only a 16-bit data bus. You should design the expansion card as a 32-bit device, but if you correctly partition the data lines and chip select lines on the card, you can use the same card in either type of machine without loss of performance. The card should have 32 data lines coming out to its connector, and the chip select lines for the upper 16 data bits and the lower 16 data bits should be separated to allow for individual selection of either the upper 16 bits or the lower 16 bits of data. The separated chip select lines are necessary for the Macintosh PowerBook 100 because it can get access to only 16 bits at a time. A 68030-based machine does not require separated chip select lines because it has a 32-bit data bus; therefore, the lines are tied back together on the computer’s main logic board.

This is gonna take some thinking about. Anybody got a handle on this paragraph? Sounds a bit like the 16 doubled up data lines are a 32bit bus if looked at in terms of a 68030 board and they would be high and low 16bit chunks to the 68HC000 of the PB100?

Trash80toHP_Mini

NIGHT STALKER

Maybe this will be closer to the way it may work. Sorted so the top set has the lower pin number for each bit.

27____D0___Data bit 0 (buffered) to and from main logic board

29____D1___Data bit 1 (buffered) to and from main logic board

31____D2___Data bit 2 (buffered) to and from main logic board

36____D3___Data bit 3 (buffered) to and from main logic board

32____D4___Data bit 4 (buffered) to and from main logic board

30____D5___Data bit 5 (buffered) to and from main logic board

28____D6___Data bit 6 (buffered) to and from main logic board

26____D7___Data bit 7 (buffered) to and from main logic board

57____D8___Data bit 8 (buffered) to and from main logic board

59____D9___Data bit 9 (buffered) to and from main logic board

61___D10___Data bit 10 (buffered) to and from main logic board

53___D11___Data bit 11 (buffered) to and from main logic board

54___D12___Data bit 12 (buffered) to and from main logic board

56___D13___Data bit 13 (buffered) to and from main logic board

55___D14___Data bit 14 (buffered) to and from main logic board

60___D15___Data bit 15 (buffered) to and from main logic board

39____D0___Data bit 0 (buffered) to and from main logic board

40____D1___Data bit 1 (buffered) to and from main logic board

37____D2___Data bit 2 (buffered) to and from main logic board

38____D3___Data bit 3 (buffered) to and from main logic board

35____D4___Data bit 4 (buffered) to and from main logic board

44____D5___Data bit 5 (buffered) to and from main logic board

42____D6___Data bit 6 (buffered) to and from main logic board

41____D7___Data bit 7 (buffered) to and from main logic board

64____D8___Data bit 8 (buffered) to and from main logic board

66____D9___Data bit 9 (buffered) to and from main logic board

68___D10___Data bit 10 (buffered) to and from main logic board

67___D11___Data bit 11 (buffered) to and from main logic board

65___D12___Data bit 12 (buffered) to and from main logic board

63___D13___Data bit 13 (buffered) to and from main logic board

58___D14___Data bit 14 (buffered) to and from main logic board

62___D15___Data bit 15 (buffered) to and from main logic board

May need to take a look at how they group on the double row connector? Dunno, it's a start. :blink:

27____D0___Data bit 0 (buffered) to and from main logic board

29____D1___Data bit 1 (buffered) to and from main logic board

31____D2___Data bit 2 (buffered) to and from main logic board

36____D3___Data bit 3 (buffered) to and from main logic board

32____D4___Data bit 4 (buffered) to and from main logic board

30____D5___Data bit 5 (buffered) to and from main logic board

28____D6___Data bit 6 (buffered) to and from main logic board

26____D7___Data bit 7 (buffered) to and from main logic board

57____D8___Data bit 8 (buffered) to and from main logic board

59____D9___Data bit 9 (buffered) to and from main logic board

61___D10___Data bit 10 (buffered) to and from main logic board

53___D11___Data bit 11 (buffered) to and from main logic board

54___D12___Data bit 12 (buffered) to and from main logic board

56___D13___Data bit 13 (buffered) to and from main logic board

55___D14___Data bit 14 (buffered) to and from main logic board

60___D15___Data bit 15 (buffered) to and from main logic board

39____D0___Data bit 0 (buffered) to and from main logic board

40____D1___Data bit 1 (buffered) to and from main logic board

37____D2___Data bit 2 (buffered) to and from main logic board

38____D3___Data bit 3 (buffered) to and from main logic board

35____D4___Data bit 4 (buffered) to and from main logic board

44____D5___Data bit 5 (buffered) to and from main logic board

42____D6___Data bit 6 (buffered) to and from main logic board

41____D7___Data bit 7 (buffered) to and from main logic board

64____D8___Data bit 8 (buffered) to and from main logic board

66____D9___Data bit 9 (buffered) to and from main logic board

68___D10___Data bit 10 (buffered) to and from main logic board

67___D11___Data bit 11 (buffered) to and from main logic board

65___D12___Data bit 12 (buffered) to and from main logic board

63___D13___Data bit 13 (buffered) to and from main logic board

58___D14___Data bit 14 (buffered) to and from main logic board

62___D15___Data bit 15 (buffered) to and from main logic board

May need to take a look at how they group on the double row connector? Dunno, it's a start. :blink:

Trash80toHP_Mini

NIGHT STALKER

Elaborating on that decoding method would be most helpful. Avoiding memory controller portion of the CPU Glu ASIC's complications and doing all memory ops directly off the 68030's internal bus would almost be too good to be true.Good thing is, the RAM could be connected to the 030, and used in 030 style decoding. Dont need the UDS/LDS 16-bit switching as needed on the standard bus, so it would be wired behind that logic.

Might need to retain the stock 2MB of PSRAM on the accelerator to POST though?

I'm VERY curious about how the Compact Mac accelerators address SIMMs on board? Can anyone clue me in on that?

Trash80toHP_Mini

NIGHT STALKER

https://www.mouser.com/pdfdocs/20503275.pdf

If anyone knows the connector type used for PowerBook processor cards, please let me know. 100 and 1400 especially.

If anyone knows the connector type used for PowerBook processor cards, please let me know. 100 and 1400 especially.

Last edited by a moderator:

Bolle

Well-known member

I'm VERY curious about how the Compact Mac accelerators address SIMMs on board? Can anyone clue me in on that?

You do remember this one right here, don't you?

4 GALs to handle everything.

Another 4 GALs for the RAM.

I think we talked about this before. RAM is sitting on the 030 bus - all 4 SIMMs have to be populated at once.

The Mac will not work without memory on the main logicboard if I remember correctly. It really shouldn't as the memory on the accelerator is software activated and only works together with Compact Virtual.

Trash80toHP_Mini

NIGHT STALKER

Sweet! Nope, I forgot about the Quesse card with that nifty RAM daughtercard. How convenient is THAT! [ ]

]

I see a tad more than the four GALs.

HCT74 - Dual D-Type Positive-Edge-Triggered Flip-Flop (if I'm misreading HC174, which is the same think in Hex)

________ probably part of the GAL based Memory Controller setup? Positioning makes me think there's nothing else on that side.

HCT245 - Octal Bus Transceiver 3-State Outputs: I see one pair, I bet another pair is hidden underneath the SIMM

________ driving/buffering that interboard connector setup on the 32 bit data bus would be my guess.

You haven't got one in your collection do you, Bolle?

Does anyone? Posting some HiRes pics of both sides sans SIMMs would be a wonderful thing.

I see a tad more than the four GALs.

HCT74 - Dual D-Type Positive-Edge-Triggered Flip-Flop (if I'm misreading HC174, which is the same think in Hex)

________ probably part of the GAL based Memory Controller setup? Positioning makes me think there's nothing else on that side.

HCT245 - Octal Bus Transceiver 3-State Outputs: I see one pair, I bet another pair is hidden underneath the SIMM

________ driving/buffering that interboard connector setup on the 32 bit data bus would be my guess.

You haven't got one in your collection do you, Bolle?

Does anyone? Posting some HiRes pics of both sides sans SIMMs would be a wonderful thing.

techknight

Well-known member

The accelerators usually used the on-board ram as a virtual memory/disk routed via the MMU.

Trash: I know the portable inside and out. Not the backlit, but the non-backlit. the MISC GLU does the bank switching/decoding for the on-board RAM. My portable, I removed the buffer ICs and changed the CPLD code on my RAM card and actually "took over" the 1MB of onboard RAM. That knocked me down to 8MB, but it ran faster as the on board-RAM is slower than what I used in my RAM card.

I also have the pinouts for BOTH LCD panels, Never got around to it, but I was going to adapt a backlit cable for a non-backlit display for testing boards.

Trash: I know the portable inside and out. Not the backlit, but the non-backlit. the MISC GLU does the bank switching/decoding for the on-board RAM. My portable, I removed the buffer ICs and changed the CPLD code on my RAM card and actually "took over" the 1MB of onboard RAM. That knocked me down to 8MB, but it ran faster as the on board-RAM is slower than what I used in my RAM card.

I also have the pinouts for BOTH LCD panels, Never got around to it, but I was going to adapt a backlit cable for a non-backlit display for testing boards.

Last edited by a moderator:

Trash80toHP_Mini

NIGHT STALKER

I'm guessing the version with the optional memory upgrade card is an early edition. PCB's (c)1990, what's the date on yours?

Any HiRes pics you can post of it would be greatly appreciated. I'm especially curious about the Bus Transceiver or lack thereof on your board. For just the SIMM interface they might not be necessary on yours, but between that and the interboard connector they'd almost certainly be required on the one above.

Any HiRes pics you can post of it would be greatly appreciated. I'm especially curious about the Bus Transceiver or lack thereof on your board. For just the SIMM interface they might not be necessary on yours, but between that and the interboard connector they'd almost certainly be required on the one above.

Trash80toHP_Mini

NIGHT STALKER

Yep, that's why I was wondering early on if the Luggable and PB100 would be compatible with Compact Virtual, given the extra memory to play with. [The accelerators usually used the on-board ram as a virtual memory/disk routed via the MMU.

That's another reason I recently figured that we couldn't do without the stock 2MB of PSRAM. It's almost certainly needed for the 68030 running in "68000 mode" to pass POST and then to set Compact Virtual in motion for addressing expanded memory.

That's exactly why I was elated to see you interested in this project. Thanks, I'd skimmed the docs on the two ASICS. I misinterpreted the verbiage and missed the thin lines connecting the entire memory subsystem to Misc.GLU:Trash: I know the portable inside and out. Not the backlit, but the non-backlit. the MISC GLU does the bank switching/decoding for the on-board RAM.

Miscellaneous GLU logic chip

The Miscellaneous GLU logic chip provides random logic functions

such as modem–serial port multiplexing, pseudostatic RAM chip

select and refresh, and the clock control logic functions associated

with the Power Manager system.

Studying the saga of your MemCard's development is definitely on my reading list. [My portable, I removed the buffer ICs and changed the CPLD code on my RAM card and actually "took over" the 1MB of onboard RAM. That knocked me down to 8MB, but it ran faster as the on board-RAM is slower than what I used in my RAM card.

Last edited by a moderator:

Trash80toHP_Mini

NIGHT STALKER

We know the PowerCache runs in the SE/30 sans mobo CPU, but does it still need a driver to let itself know that it's NOT just the stock CPU? I always figured the drivers were only needed to set up the Cache?

I've been guessing that the Performer will run in place of the 68000 at boot time, but it will still need drivers to let it know it's a 68030, not the stock 68000? I'm wondering if the "Mac" only sees the Performer as a fast 68000 if it's installed in place of the CPU without driver support?

Do Socketed and PDS adapted PowerCache accelerators use the same drivers? If so, is there a mechanism to let the driver know not to shut down the stock CPU for one and to do so for the other?

Is it as simple as grabbing hold of one of the stock processor's control lines and not letting go? Getting mixed up a bit, but ISTR something like that being mentioned somewhere. :blink:

Wondering if the Performer might hang when there's no longer a stock CPU to shut down?

I've been guessing that the Performer will run in place of the 68000 at boot time, but it will still need drivers to let it know it's a 68030, not the stock 68000? I'm wondering if the "Mac" only sees the Performer as a fast 68000 if it's installed in place of the CPU without driver support?

Do Socketed and PDS adapted PowerCache accelerators use the same drivers? If so, is there a mechanism to let the driver know not to shut down the stock CPU for one and to do so for the other?

Is it as simple as grabbing hold of one of the stock processor's control lines and not letting go? Getting mixed up a bit, but ISTR something like that being mentioned somewhere. :blink:

Wondering if the Performer might hang when there's no longer a stock CPU to shut down?

Last edited by a moderator:

Similar threads

- Replies

- 58

- Views

- 10K

- Replies

- 23

- Views

- 2K

- Replies

- 105

- Views

- 16K