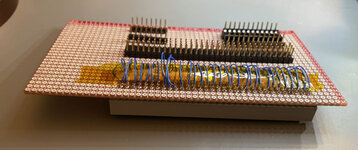

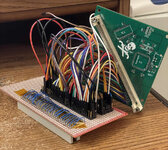

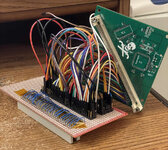

So...I have an update on this Flasher utility saga. I spent all day putting this together. I think this may be the jankiest LC PDS card ever created.

It brings out all 96 pins to a 3x32 header so I can attach jumpers. I don't need the extra 18 pins that newer models have. My PDS card also has a socket for a GAL22V10, headers for running jumpers to it, and a few small headers meant for 5V and GND. If you ever plan on doing this...just design a PCB. Don't do what I did. This took hours and hours to solder. It wasn't fun. But I had no choice...my free time is now, and a PCB would take too long to arrive.

I populated it with the bare minimum needed to make the CPU happy and programmed an ATF22V10C with my final design for acknowledging reads and writes sent to the PDS socket. Basically listening to a few address lines, R/W and /AS, and controlling /DSACK0 and /DSACK1 as necessary.

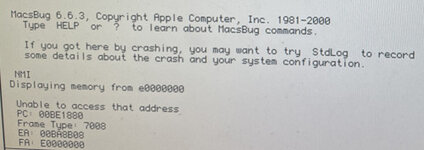

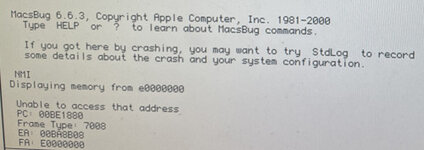

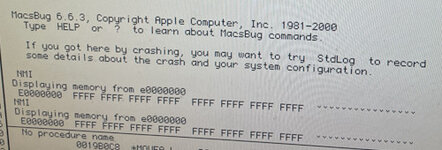

This worked. With nothing installed, reads to the PDS memory area result in a bus error:

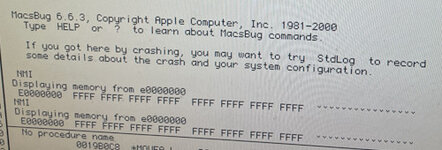

With my card installed, I read junk data of all 0xFF instead, meaning my PLD is doing its job!

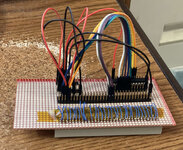

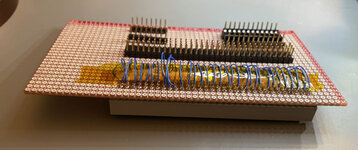

So...you think my card looks crazy? You ain't seen nothing yet. Here's crazy:

This is one of my bare programmer PCBs with jumper wires soldered and connected everywhere on my PDS card so bring out all the correct pins exactly where they go. All of the address and data lines of the SIMM socket go directly to the PDS connector. /OE and /WE go to the PLD -- it controls them with the right pattern when there's a matching read or write cycle. I also brought 12V to the SIMM socket for VPP for the Lobos board replica. Luckily, I already had this bare socket-to-jumper-wires adapter board from when I was working on the next-generation SIMM programmer. It was still a huge pain and took hours to get all of the wires hooked up!

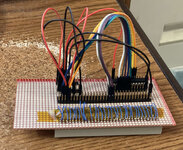

Finally, it was time to insert one of my replica Lobos SIMMs and plug it into my LC 475 to see what happens. First, I made sure 12V wasn't accidentally shorted anywhere else on the board. That would be bad.

Yeah...janky is definitely the right word to describe this setup! The corner of the bare programmer PCB is balancing on the CPU. Everything booted, which was a good sign. It meant I wasn't screwing up the address and data lines. Then I opened up Flasher, and...

It works! The right side of the Flasher UI is populated with SIMM info. I can dump, program, and verify through it! This SIMM had a different image on it (I think it's my hacked 630 ROM with the 6200 chime). I was able to dump the 475's onboard ROM and program it to the SIMM through the PDS card, and everything worked perfectly!

I already got some hints about the purpose of the PDS card on my blog, so I'm kind of repeating what I already knew at this point, but these tests definitely confirm that the PDS card was meant for programming SIMMs (you wouldn't be booted from the PDS card). When you program a ROM image through this PDS card, the UI updates as you do it. It tells you that it's erasing, then programming, then verifying. Onboard SIMM programming didn't allow this, because you can't do toolbox calls while you're in the middle of programming the ROM you're booted from. Also, it just leaves you back in the UI when it's done -- no reboot like when you program the SIMM you're booted from. The status says "Successful" afterward.

So...I had to learn all about 680x0 bus cycles, how to program PLDs in WinCupl, tediously solder a whole bunch of wires, then tediously hook up a bunch of jumper wires that were way too short. But it was totally worth it! I have now proven the concept of a PDS SIMM programmer card. I think it may be worth it to design something a bit cleaner that's an actual PCB. If it could be small enough to fit in the 575, 580, and 630 it should work in them too.

This same approach should work for other 040 PDS slots too. The 610 might be the easiest since it has the funky card edge connector slot which I think would be super simple to make a board to plug into. The others would need the full 040 PDS connector which I know is harder to find. I think the PLD would have to be slightly more complicated too -- the LC PDS slot's read/write cycles are slow enough that I didn't have to do anything special with wait states to access 120 ns flash chips, but I'm pretty sure the direct 040 PDS would be too fast so I'd have to slow it down a bit. Nothing too crazy though...I think...

This is pretty exciting! It's the equivalent of my USB SIMM programmer, but Apple made software for using it and it's a PDS card instead!