I've been tinkering a lot with ROM SIMMs and Quadras lately. As a quick summary, most Quadras (maybe all of them?) seem to have been designed to work with a ROM SIMM. They generally have soldered ROMs and in most cases, especially on newer Quadras, the socket isn't populated.

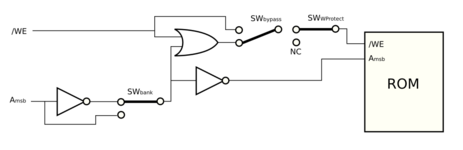

@Performa450 shared pictures of this Lobos board ROM SIMM he bought a couple of years ago. I thought it was cool, and in that thread I even figured out that it was programmable and the programming voltage (VPP) and write enable (/WE) pins were brought out to the ROM SIMM socket (pins 2 and 3, respectively).

I didn't make the connection until recently when the @Jockelill started trying to get ROM disks working on Quadras, but the logic boards of the era seem to have 12V available for VPP on pin 2, and pin 3 is routed to whatever Apple ASIC is responsible for address mapping. I've physically confirmed this on my LC 475, Centris 610, Performa 630, and Quadra 660av. And it's becoming more and more clear that they're hooked up in general like this. What this means is...the Quadras were able to program their own ROM SIMMs in-system during development.

A couple of people have recently sent me a link to this Apple Flash ROM Utility on the Macintosh Garden. According to the description it came from a prototype PowerBook 520. I've been spending a bunch of time inspecting the code in this utility and disassembling it to understand it better. I've found several things that I thought would be interesting to discuss here, and I plan on updating this thread as I find more stuff.

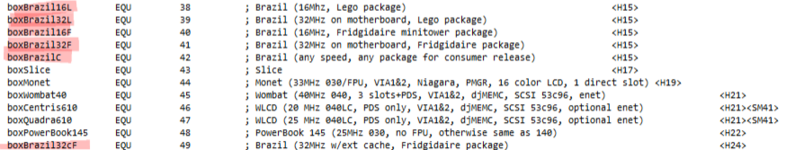

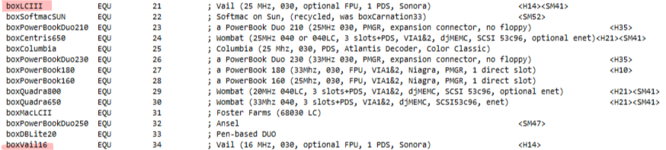

It supports programming flashable ROMs in the following Macs. I'm listing them in separate groups just like how they're arranged in the code, to perhaps provide some extra context about what the unknown machine IDs might be similar to:

@Performa450 shared pictures of this Lobos board ROM SIMM he bought a couple of years ago. I thought it was cool, and in that thread I even figured out that it was programmable and the programming voltage (VPP) and write enable (/WE) pins were brought out to the ROM SIMM socket (pins 2 and 3, respectively).

I didn't make the connection until recently when the @Jockelill started trying to get ROM disks working on Quadras, but the logic boards of the era seem to have 12V available for VPP on pin 2, and pin 3 is routed to whatever Apple ASIC is responsible for address mapping. I've physically confirmed this on my LC 475, Centris 610, Performa 630, and Quadra 660av. And it's becoming more and more clear that they're hooked up in general like this. What this means is...the Quadras were able to program their own ROM SIMMs in-system during development.

A couple of people have recently sent me a link to this Apple Flash ROM Utility on the Macintosh Garden. According to the description it came from a prototype PowerBook 520. I've been spending a bunch of time inspecting the code in this utility and disassembling it to understand it better. I've found several things that I thought would be interesting to discuss here, and I plan on updating this thread as I find more stuff.

It supports programming flashable ROMs in the following Macs. I'm listing them in separate groups just like how they're arranged in the code, to perhaps provide some extra context about what the unknown machine IDs might be similar to:

- All of these 040 machines are grouped together, and also support flashable PDS cards:

- Quadra 700, 900, and 950

- Centris/Quadra 610/650, Quadra 800

- LC 475/Quadra 605

- LC 575

- 630

- 580

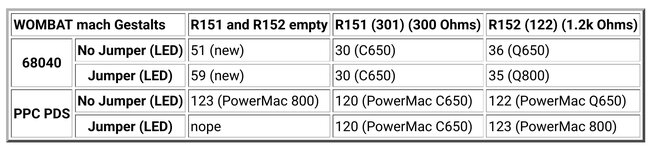

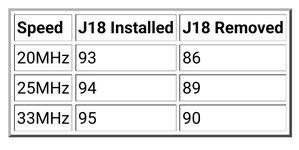

- Unknown gestalt machine IDs 51, 57, 58, 59, 63, 86, 87, 90, 91, 93, 95, 96, and 97

- A lot of these gestalt IDs appear to have been later repurposed for the Power Macs, but in this utility I'm pretty sure they represent older unreleased machines. There's a lot of 68k-specific code in the flashing routines for stuff like MMU config that I'm pretty sure wouldn't work in a PowerPC Mac.

- The LC III is by itself with another unknown machine ID:

- LC III (maybe an earlier prototype version that had a ROM SIMM socket?)

- Unknown machine ID 40 -- seems to be another 030-based machine of some sort.

- The AV machines are grouped together by themselves:

- 660av/840av

- Unknown machine IDs 43 and 79

- These 030-based Macs are grouped together:

- IIvx/IIvi/Performa 600

- Unknown machine IDs 46, 47, and 55

- PowerBook Duos are grouped together and in some cases have a ROM type referred to as "DBLite Flash":

- PowerBook Duo 210, 230, 250, 270c, 280, 280c

- Unknown machine IDs 39 and 76

- More PowerBooks that use a "Dartanian Flash":

- PowerBook 160

- PowerBook 165c

- PowerBook 180

- The 180c is interestingly missing from this list...

- These machines are grouped together and use a "Slice Flash":

- Color Classic

- Mac TV (again, no ROM SIMM...maybe an earlier board revision?)

- Another group of machines that are similar to the above and also use "Slice Flash", but with a different ROM base address:

- LC 520

- LC 550

- Unknown machine IDs 81 and 83

- Final group that uses "Blackbird Flash" or "Malcolm Flash":

- PowerBook 500

- Unknown machine ID 73

- Am28F020

- It even seems to have support for a PDS card that has 16 of these chips onboard, which would result in a whopping 4 MB of ROM space

- Am29F020A

- Intel 28F020

- Intel 28F010 (mistakenly identified by a string in the software as 28F256)

- Intel 28F008SA