With some spare time at hand, I've taken upon the task of determining whether or not the MicroMac Performer 68030 upgrade for the Macintosh SE can be installed directly to a DIP64 socket on the motherboard rather than the using the SE PDS slot. This would be similar to operation on a Macintosh Plus, except rather than piggyback onto the stock 68000, the 68000 would be completely removed.

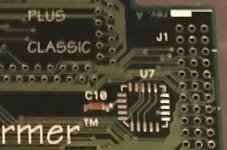

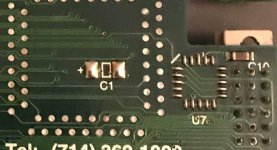

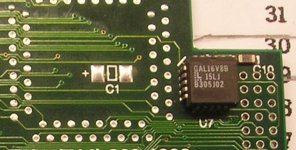

I have two of these cards, and this one will serve as the test subject on a second Macintosh SE motherboard:

Tonight's goal was to remove the PDS connector from the accelerator card and to remove the 68000 from the motherboard. The first task was pretty straightforward, although a few of the pins had to be tugged on a bit to allow the connector to separate from the board:

On the SE, the 68000 is not socketed, so some work had to be done to remove that:

Even with a desoldering gun, I had to sacrifice the 68000 due to growing impatience:

I test-fit some new DIP64 sockets on the motherboard and the Performer. Too late to solder them in, but looking good so far:

Before I started, I was able to determine the proper alignment of the Performer to the 68000 pins on the motherboard, and a test fit (sans header pins) looks good so far:

There is about 2mm of clearance from the edge of the board to the brown socket on the left in the image, and with with 1x32 header pins installed to connect the accelerator to the motherboard that clearance will grow to about 3-4mm or so. Still should be lower than it was when connected to PDS slot.

I am waiting for the header strips to arrive from eBay/China sometime this coming week, and hope to have some good news then. Worst case scenario, I can solder the strips to another 68000 if it does in fact need to be there. The one thing that might really hold up the success of this test is the lack of a GAL at U7. The Macintosh Plus version of this board has that GAL populated, so it may be necessary when PDS isn't used, I'm not sure. I have not seen a Classic version to know if U7 is there or not.

My two SE boards here:

I have two of these cards, and this one will serve as the test subject on a second Macintosh SE motherboard:

Tonight's goal was to remove the PDS connector from the accelerator card and to remove the 68000 from the motherboard. The first task was pretty straightforward, although a few of the pins had to be tugged on a bit to allow the connector to separate from the board:

On the SE, the 68000 is not socketed, so some work had to be done to remove that:

Even with a desoldering gun, I had to sacrifice the 68000 due to growing impatience:

I test-fit some new DIP64 sockets on the motherboard and the Performer. Too late to solder them in, but looking good so far:

Before I started, I was able to determine the proper alignment of the Performer to the 68000 pins on the motherboard, and a test fit (sans header pins) looks good so far:

There is about 2mm of clearance from the edge of the board to the brown socket on the left in the image, and with with 1x32 header pins installed to connect the accelerator to the motherboard that clearance will grow to about 3-4mm or so. Still should be lower than it was when connected to PDS slot.

I am waiting for the header strips to arrive from eBay/China sometime this coming week, and hope to have some good news then. Worst case scenario, I can solder the strips to another 68000 if it does in fact need to be there. The one thing that might really hold up the success of this test is the lack of a GAL at U7. The Macintosh Plus version of this board has that GAL populated, so it may be necessary when PDS isn't used, I'm not sure. I have not seen a Classic version to know if U7 is there or not.

My two SE boards here: