I skimmed through this quickly so let me share what I know about this stuff, starting with the FC3 signal and the 24/32 bit LC address maps.

The original Mac LC had a 68020 and no MMU. Although the addressing capability of the 68020 is 32 bits, a scheme like in the Mac II is used, where the top 8 address bits are ignored to make the system compatible with 32-bit-dirty software. Unlike the Mac II, however, there is no "Apple HMMU" chip which performs the address translation. Instead, the FC3 signal is high only when the system is operating with 32-bit addresses on the physical bus. Decode logic in the onboard chipset and expansion cards must use the FC3 signal to decide whether to decode an address as a 32-bit address, or whether to ignore the top 8 bits and treat it as a 24-bit address. The later LCs had 68030s with an integrated MMU. They always configure the integrated MMU to output 32-bit addresses onto the bus. Thus the FC3 signal is always driven high in the later LCs. This is shown here in the block diagram of the LC:

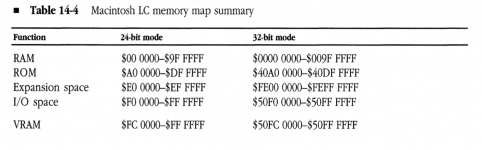

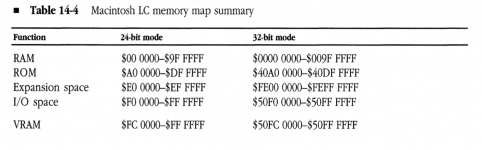

One more thing about the LC PDS and the LC series' address map. The earlier LC PDS machines have a 96-pin connector that does not carry the entire address bus. The LC III and the 68040 LCs added another little connector below to accommodate more address lines (and thus a larger main memory capacity). Looking at the LC's address map, you can see that given a 32-bit address, the device to be accessed can be uniquely identified by A31 and A23..0:

So the consequence is that some signals between A31 and A23 can be left off of the PDS connector. In particular, A31 and A27..A0 are sent to the LC PDS card, with A30..28 excluded.

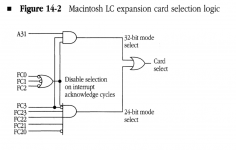

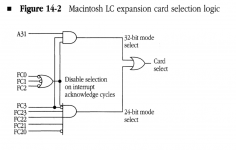

On an LC PDS card, here is the circuit to generate the card select signal, as you can see, totally independent of A30..A24:

To interface an LC PDS card to an SE/30, the solution goes something like this. We must run in 32-bit mode by tying the LC PDS card's FC3 high. Like the later LCs, the SE/30 only outputs 32-bit addresses onto the bus, as the 24-to-32 translation is done internally in the 68030's MMU. Then we map SE/30 address $FCXXXXXX to $FEXXXXXX on the card by inverting A25.

Also, since in 32-bit mode, the selection of the LC PDS card can be done based just on A31, we must also gate A31 such that A31 is 0 when an address not of the form $FCXXXXXX is on the Mac side of the address bus. When the LC PDS card does DMA, we must send back what it drives onto the address bus exactly, with no inversion. We also need to send A30..28 back to the SE/30, since the LC PDS card does not have those pins. DMA devices rarely access peripherals, so we will reconstruct A30..28 as if the LC PDS card is commanding an access to RAM. If we send back all 0's for A30..28 during a DMA transfer, this forces an access into the range of either $0XXXXXXX or $8XXXXXXX. $8XXXXXXX is NuBus extended slot space in the SE/30, which is empty, and also an LC PDS card is unlikely to perform a DMA access with A31 set, since that means the card would be trying to access itself using DMA. $0XXXXXXX refers to the first 256MB of the 1GB assigned to RAM in the SE/30. Since the SE/30's memory controller can only address 128MB, we're good.

I wrote a tiny bit of PALASM which should allow you to accomplish this in a GAL:

Code:

;PALASM Design Description

;---------------------------------- Declaration Segment ------------

TITLE LC to SE30

PATTERN

REVISION 0.1

AUTHOR Zane Kaminski

COMPANY Garrett's Workshop

DATE 07/19/19

CHIP _LCTOSE30 PALCE16V8

;---------------------------------- PIN Declarations ---------------

PIN 2 /BGACK ;

PIN 3 MacA27 ;

PIN 4 MacA26 ;

PIN 5 MacA24 ;

PIN 12 MacA25 COMBINATORIAL ;

PIN 13 CardA25 COMBINATORIAL ;

PIN 14 CardA31 COMBINATORIAL ;

PIN 15 MacA31 COMBINATORIAL ;

PIN 16 MacA30 COMBINATORIAL ;

PIN 17 MacA29 COMBINATORIAL ;

PIN 18 MacA28 COMBINATORIAL ;

;----------------------------------- Boolean Equation Segment ------

EQUATIONS

; During DMA, output A30..28 = 0, A25=A25, A31=A31 back to Mac

MacA31 = CardA31

MacA30 = 0

MacA29 = 0

MacA28 = 0

MacA25 = CardA25

MacA31.TRST = BGACK

MacA30.TRST = BGACK

MacA29.TRST = BGACK

MacA28.TRST = BGACK

MacA25.TRST = BGACK

; When DMA not occurring, output inversion of MacA25 to LC PDS card

; and gate CardA31 with MacA==FCXXXXXX

CardA31 = MacA31 * MacA30 * MacA29 * MacA28 * MacA27 * MacA26 * /MacA25 * /MacA24

CardA25 = /MacA25

CardA31.TRST = /BGACK

CardA25.TRST = /BGACK

;-------------------------------------------------------------------

Try compiling that with PALASM in DOSBOX. Maybe there are some mistakes but the idea is right, I think. You could also try to work in a more sophisticated IRQ scheme into the PAL somehow. There is one spare output pin in the GAL16V8 so hopefully you can fit it all in the little GAL. Otherwise try the GAL22V10 or a larger CPLD like an Atmel ATF1500-series or an Altera MAX7000S-series.