No idea. I have decided to put SE/30 on hold for now as well. The SE design is too young and unstable to turn it into a "master schematic" and fork that for each supported machine. That's what I was trying to do in the past few days, but when the schematic is changing so fast, that's a pain.

The only commitment I can make relating to the schedule is that I'll spend a lot of my spare time on the project haha. This is, for me, a learning experience, so I may make a ton of mistakes and it may take a while. I think that the only way these types of projects are completed are by someone who is in it more for the learning than to have the final product, y'know the super Mac or whatever.

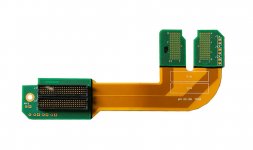

About the boards, I'll definitely release all of the source files eventually, so you could go yourself to OSHPark or some other board fab and purchase the board yourself, solder the components on, program the FPGAs over JTAG (current design has a system controller that can bit-bang JTAG to update the FPGA software, but I don't plan on implementing that, so you will need an external programmer), and put the Snapdragon in the socket, and use a microSD card with the software I'll provide to boot the Snapdragon up.

Now, for at least SE, maybe more models, I will probably sell fully assembled units myself. I have explicitly avoided BGA parts, so I will be able to reflow the boards myself or hire a friend skilled in that stuff to do it. In order to do this, however, I will have to have a Kickstarter or something to raise the funds required to build the boards. If more than 25 or 40 boards are in demand, I will outsource production to China, since that's around when it becomes affordable.

Gotcha! One other thing though, was wondering if you knew that when you're designing for the SE, you're also designing for the Plus and the Classic. If you have room on your board to parallel your SE EuroDin PDS connector with thruholes for a 68000 socket as shown, you're also tripling your user base. Now as then, in terms of development it's all about economies of scale.

Since your board's profile will undoubtedly be far lower than that of this MicroMac accelerator, the CPU/PDS interface adaptation could probably be done with a directly soldered header interconnected daughtercard underneath your PDS card.. It'll be interesting to hear from techknight if something similar might be possible for the Portable's CPU interface.

One wonders if the marvels of rapid prototyping might pave the way for a reproduction of the Killy Klip interconnect hardware for this and many other 68000 board installations?

It's tempting, but there are a few notable electrical differences.

Firstly, the SE has this scheme where the ~8 MHz clock is like 90 degrees out of phase of the ~16 MHz clock from which it is generated. I don't think the 128k - Plus do that.

If we replaced the 68000, we would also have to generate ECLK. Clock routing is a pain, though the E clock is only 783 kHz, so that's in no way fast, but in general, clock routing is a pain and doing it improperly is a common source of problems. In the last schematic I posted, I had the clocks connected to the system controller, thinking that it might be useful to measure their frequency or run synchronous to them or something. I have since removed that feature. Maybe in the SE/30 design, the system controller will have to take in the 16 MHz clock and make 32 MHz from it, from which the FPGA control logic will run, but no need to complicate things for the SE.

It is tempting to try and copy the shape of that MicroMac card, though... hmm. The mechanical engineering part of it, making sure it fits properly, is really not one of my strong areas. Also mine may be thicker than the traditional accelerators. The snapdragon module is a few millimeters tall, just like the 68030 on that board you posted.

Maybe once I have it all together for SE, I can try adding those extra pins, but I'm already wrestling with a lot of complexity as it is. The cost of the boards is also not going to be that much if I can manage to buy 25 or so boards for each supported machine. See my reply to asaggynoodle above about how I plan to build them.