I have reworked my design. The major changes are:

- Processor board (Snapdragon 410E) sourced externally, not designed by me

- FPGA has been eliminated

- No USB 3.0

- Has microSD slot on accelerator board

- Small CPLD implements interrupt priority control

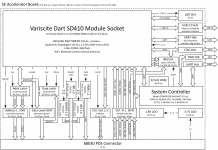

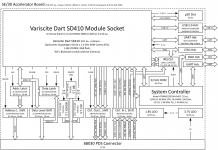

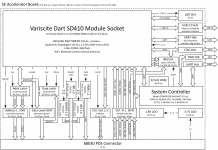

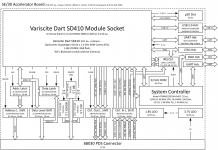

Here are the block diagram pictures for SE and SE/30. There is a lot more detail about the bus signals now... I've figured that aspect out pretty fully.

The benefits are lower cost, faster processing, and less special software that must be written.

I decided to go with the Snapdragon 410E, but it was impossible for me to get on a board at a reasonable price. Luckily, Variscite sells the Dart SD410 module, which has the 410E, associated power management IC, 1 GByte LPDDR3, 8 GBytes eMMC flash, ad WiFi, Bluetooth, GPS, FM radio capability (external antenna needed).

The SD410 module will be mounted on the board with two connectors that are about $1.50 each. It’s also half the size of a DDR2 SODIMM.

I’ve eliminated the FPGA and now am using the SD410’s GPIO and some latches and level-shifters to implement the bus interface.

Since the FPGA was supposed to be a QFP-type part, not BGA, this and the smaller processor module will allow us to greatly reduce the size of the main board.

I think that the Snapdragon can run a custom-rolled version of Linux. The details of the Snapdragon 410E are so complicated, secret, and proprietary, that if we ran our code bare-on-the-metal or rolled our own RTOS, we would be missing out on so many capabilities and the benefits of fully-developed driver software.

The WiFi and Bluetooth functionality on the SD410 module are two obvious things we’d be missing without using Linux. However, the use of Linux will allow individuals who are more experienced in Linux system administration, rather than system design, programming, EE, etc., to contribute and make the Maccelerator better.

Now, in order to run Linux, the accelerator process which actually executes the code must run as some kind of a driver so that it can directly manipulate the GPIO pin control I/O registers without needing to perform a context switch. Either that or the emulator can run in userspace and just the bus stuff can run as a driver. That’s the correct way to do it, but I’m trying to achieve the best performance possible with the amount of time and money I can devote to the project. We will see.

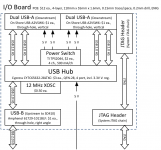

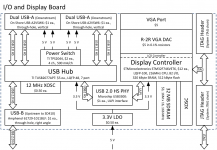

Since we’re running Linux, there is less of a need for the I/O board, especially if we can get the SD410’s WiFi and Bluetooth working. The I/O board also is a bit mechanically difficult, in terms of the amount of room available for it. Rather than the I/O board, a much cheaper option would be to just run USB to the back of the Mac. Nonetheless, I/O boards will still be supported.

Anyway, here’s a rough bil of materials (for SE/30):

Variscite Dart SD410 (Processor Board) 1 x $57 = $57

Hirose DF40C-90DS-0.4V (SD410 conn.) 2 x $1.50 = $3

Euro-DIN 120 (PDS Connector) 1 x $7.50 = $7.50

Atmel SAMD10D14 (System Controller) 1 x $2 = $2

Lattice LC4032ZE (IRQ Controller) 1 x $1 = $1

microSD slot est. = $2.50

16-bit latch 4 x $0.50 = $2

16-bit level shift 6 x $1.50 = $9

1-bit level shift 3 x $0.50 = $1.50

32.768 kHz crystal oscillator 1 x $0.50 = $0.50

Power stuff (L, bypass C, V. regs.) est. = $5

PCB est. = $15

This stuff totals $106. This is without a doubt an underestimate of the final cost (assembly, shipping, packaging, etc. not included), but we should be able to it out the door for under $150, as long as 15 or so people want one. I will work on making it even cheaper.