Regarding the sRsrc format, for the Stock 1280x960, here is what I see by attempting pattern-matching vs. obvious data types and working forwards/backwards, etc.:

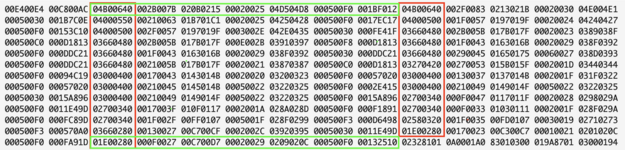

original data: [00000076 1F320000 50020600 4F010101 000F001E 00BE00C9 0002002D 03ED03F0 FFFFFFFF 00E7FFFF 0000FFFF 00000000 00000000 00404000

05508005 05000000 E0C0B576 256D0000 00000040 00810073 00000500 03C09500 53757065 724D6174 63682048 6967682D 52657320 32302043 6F6C6F72 00]

00000076: sRsrc length (from earlier post)

1F: clock select (from earlier post)

looking for start of SMT -- HES should be a low value, then HEB, HSB, HTot, [?], VES, VEB, VSB, VTOT and they must be word values that make sense.

320000 - working backwards from the start of SMT and likely BSR, these must be board-related - there were 2 registers, but there is a byte missing - oh frequency select above - right. So -- should probably look like this:

Reg 1:

1F - clock select

32 - ? (do more comparisons on this one)

Reg 2:

00 - ?

00 - ?

I guess that makes sense.

BSR -- see reasoning below - 8 bytes and obvious start of timing data for SMT...but ??

50

02

06

00

4F

01

01

01 (this data doesn't fit timing values, so may be BSR - it had 8 byte registers)

next block of data that looks like valid SMT word timing values (000F 001E 00BE 00C9 0002 002D 03ED 03F0 FFFFFFFF 00E7FFFF 0000FFFF 00000000 00000000 00404000

05508005 05000000 E0C0B576 256D0000 00000040)

SMT02 offset in the sRsrc -- So -- byte 16, or $10 is the start of SMT02 data -- but I guess you already figured that out

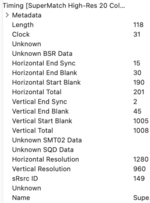

000F (15) - must be HES -- first low word value

001E (30) - HEB

00BE (179) - HSB

00C9 (201) - HTOT

0002 (2) - must be VES - looks right

002D (45) - VEB (low number)

03ED (1005) - VSB = VRES(960) + VEB(45) - seems OK, off by 1?

03F0 (1008) - VTOT = VRES(960) + VEB(45) + VES(2)

No apparent counter registers in the timing block above.

Other SMT02 registers - this is the "deer with no eyes" section.

FFFF

FFFF

00E7

FFFF

0000

FFFF

0000

0000

0000

0000

0040

4000

0550

8005

0500

0000

E0C0

B576

256D

0000

0000

0040

Next part: 00810073 0000

Must be SQD, since it had 3 registers, it's the only thing left and the sRsrc/name info follows. So...ruling out, etc. Best fit. Easy enough to check - write garbage there and if the acceleration is all screwed up, then you know.

0081

0073

0000

This is the ending part, which is pretty easy based on the obvious data:

0500 1280 hRes

03C0 960 vRes

95 master sRsrc ID

00 padding probably

53757065 724D6174 6368

2048 696768

2D 526573

20 3230

2043 6F6C6F72

00 [term]

Supe rMat ch H igh- Res 20 C olor

So, then the question is...does your modification make sense re: timing? Let's see -- as you mention, the timing should be similar.

000E/HES: 14 (you could try starting with the same H values and just modify V)

0014/HEB: 20

00B4/HSB: 180

00D3/HTOT: 211

0003/VES: 3 (I would leave this value at 2 -- it's going to be SMT-related)

0004/VEB: 4 (no - back porch is too small (may be slammed against the top of the monitor-- proportionally, maybe

42 vs. 45 (6.7% decrease) -- or ask Douglas Adams

)

0404/VSB: 1028 (no - 1024 + 42 -- 1066, as above or maybe 1067 -- try $042A)

042A/VTOT: 1066 (no - 1024 + 42 + 2 +1 = 1069 -- so $042D)

These are my best guesses -- maybe not right -- you will have to play around with it and see.

Also, in your version, it doesn't look like you modifed the screen resolution at the end of the sRsrc.

Vertical $03C0 (960) should be $0400 (1024). This issue may be why you don't see the full height...and it should match the resolution shown in all the other related sRsrc table entries (bit depths, etc.)

OK - that's the best I can do -- hope it helps. I have to find my board...but maybe the above will help you get closer to the finish line. I think I feel like I have a video hangover.

Oh - the other questions --

Loading from SuperVideo -- maybe...but probably in the ROM. SuperVideo shows all of the available configs. And, when you use SuperVideo to change a config, it copies the data into PRAM. So, if you trace it after setting it, you can see where the config data is coming from. Or, look at SuperVideo with ResEdit when you open that screen and see what resources it is getting to track down any that might have video configuration data. But, it's possible that SuperVideo 3.0 could be inserting something into PRAM. Check the ROM carefully.

In terms of undoing things, SuperVideo will just grab what's in ROM, so it shouldn't affect what you've done unless that specific timing configuration has been replaced in software...but seems unlikely, since it would have had to work from ROM at FCS.