quorten

Well-known member

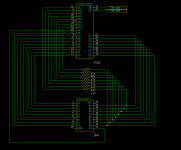

So close... I have to say I have high hopes about this. Relating to the previous discussion about the BBU pinout, it looks like it's all correct on the actual board design, Sprint Layout's misclassification of MBRAM and ROW2 was due to the fact that these are connected to pull-up resistors. Also, another note, I did find the SE PDS pinout and verified it was correct in my retrace of the schematic (one rename but otherwise good).I got all excited....plugged it in and...the PSU is dead in my SE chassis

Last edited by a moderator: