Trash80toHP_Mini

NIGHT STALKER

Yet another crazy hack that's waaaay over my head . . . probably! It's looking a bit different with current ProtoBoard technology.

Back in 2013 I got it stuck in my head that my 16MHz 68030 MicroMac Performer might be shoehorned into the Macintosh Portable:

MacintoshPortable Slot Hackage

Back in 2015 techknight got the bug to build a dedicated accelerator for the Portable

mac portable accelerator

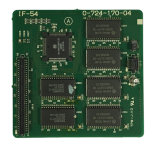

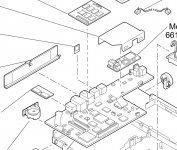

Here's the version of the Performer for the SE:

View attachment 19259

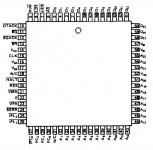

Mine's for the Mac Plus, so the EuroDin connector in uninplemented, direct 68000/Killy Klip interface is present and the unimplemented GAL at U7 is populated. This version has the QFP-132 68030 installed where mine is in the standard PGA package.

Total component count on my board for the unbuffered 68000 legs/PDS:

68030

Crystal

5 GALs

68882 Socket

PGA-68 thruholes for who knows what? 68000 PDS passthru?

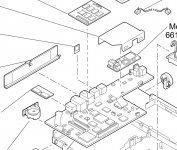

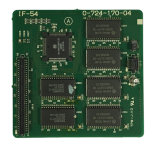

Enter the PB100 processor/ROM/PSRAM (2MB) on the PowerBook 100 Daughtercard:

68000 is a smaller QFP, the same as the QFP-132 68030 on the Performer/SE above. The Processor Card is lower than the RAM expansion Card, so the Accelerator could overlap its real estate, providing for the full 8MB RAM allotment for the PB100 on a single daughtercard.

Wasn't sure if the larger QFP-132 would fit in cubic underneath the board occupied by the QFP-68 68000, but found that may not matter.

There's a KBD support on the solder side of the PB-100 Daughterboard which may indicate that there is room to do a double sided design providing somewhere between 250% and 300% of the original PCBs single sided real estate. There are also SMT Pads for the two board interconnects on the solder side of the Daughterboard indicating that stacking another PCB on top of it may have been considered.

Dunno, we'll see. The SE/Plus/Classic Performer doubles the host's clock, raising the local bus of the 68030 to 16MHz.

The PB100 clock is already at 16MHz. ROM & RAM look to be located on the Daughtercard's local bus. Enter the MC68030FE33B-QFP-132:

@tk: these puppies have gone down to $14 ea. on eBay. [ ]

]

Insane WAG of the week would be that the proposed 68030 PowerBook 100 Accelerator would be running at 32MHz and that ROM and RAM would be along for that faster ride on its local bus?

Dunno, is there a memory controller on the PB100 main board? Moving the five existing GAL ICs to the prototype would seem to be the thing to do. Maybe tweak the oscillator value? Might the same clock on the accelerator also double the 16MHz rate of the host?

Coffee's kicking in so I'm losing my train of thought. :blink:

33MHz 68030/68882 FPU/8MB RAM infused PowerBook 100 anyone?

Comments please!

edit: forgot to mention that it would appear that none of the limitations of the Portable's PDS are present on the board interconnects of the PowerBook 100 CPU/ROM/PSRAM daughterboard. [ ]

]

edit: one last thing, since the native 68000 the Performer's Driver needed to disable would be missing from the accelerator, might the 68030 accelerator "just work" as is the case for a Sonnet CrescendoPB's G3 accelerator replacement of the 1400's Processor Daughterboard? Avoiding INIT/Driver foibles would be very cool indeed! Potentially a far more simple prospect than adapting the Performer setup to the Portable's PDS.

Back in 2013 I got it stuck in my head that my 16MHz 68030 MicroMac Performer might be shoehorned into the Macintosh Portable:

MacintoshPortable Slot Hackage

Back in 2015 techknight got the bug to build a dedicated accelerator for the Portable

mac portable accelerator

Here's the version of the Performer for the SE:

View attachment 19259

Mine's for the Mac Plus, so the EuroDin connector in uninplemented, direct 68000/Killy Klip interface is present and the unimplemented GAL at U7 is populated. This version has the QFP-132 68030 installed where mine is in the standard PGA package.

Total component count on my board for the unbuffered 68000 legs/PDS:

68030

Crystal

5 GALs

68882 Socket

PGA-68 thruholes for who knows what? 68000 PDS passthru?

Enter the PB100 processor/ROM/PSRAM (2MB) on the PowerBook 100 Daughtercard:

68000 is a smaller QFP, the same as the QFP-132 68030 on the Performer/SE above. The Processor Card is lower than the RAM expansion Card, so the Accelerator could overlap its real estate, providing for the full 8MB RAM allotment for the PB100 on a single daughtercard.

Wasn't sure if the larger QFP-132 would fit in cubic underneath the board occupied by the QFP-68 68000, but found that may not matter.

There's a KBD support on the solder side of the PB-100 Daughterboard which may indicate that there is room to do a double sided design providing somewhere between 250% and 300% of the original PCBs single sided real estate. There are also SMT Pads for the two board interconnects on the solder side of the Daughterboard indicating that stacking another PCB on top of it may have been considered.

Dunno, we'll see. The SE/Plus/Classic Performer doubles the host's clock, raising the local bus of the 68030 to 16MHz.

The PB100 clock is already at 16MHz. ROM & RAM look to be located on the Daughtercard's local bus. Enter the MC68030FE33B-QFP-132:

@tk: these puppies have gone down to $14 ea. on eBay. [

Insane WAG of the week would be that the proposed 68030 PowerBook 100 Accelerator would be running at 32MHz and that ROM and RAM would be along for that faster ride on its local bus?

Dunno, is there a memory controller on the PB100 main board? Moving the five existing GAL ICs to the prototype would seem to be the thing to do. Maybe tweak the oscillator value? Might the same clock on the accelerator also double the 16MHz rate of the host?

Coffee's kicking in so I'm losing my train of thought. :blink:

33MHz 68030/68882 FPU/8MB RAM infused PowerBook 100 anyone?

Comments please!

edit: forgot to mention that it would appear that none of the limitations of the Portable's PDS are present on the board interconnects of the PowerBook 100 CPU/ROM/PSRAM daughterboard. [

edit: one last thing, since the native 68000 the Performer's Driver needed to disable would be missing from the accelerator, might the 68030 accelerator "just work" as is the case for a Sonnet CrescendoPB's G3 accelerator replacement of the 1400's Processor Daughterboard? Avoiding INIT/Driver foibles would be very cool indeed! Potentially a far more simple prospect than adapting the Performer setup to the Portable's PDS.

Last edited by a moderator: