First resolution-changing experiments!

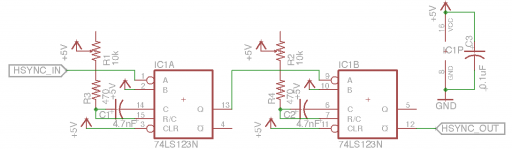

I decided the best way to test different resolutions with the existing display was to keep the 1-bit video circuits for now and build a high-speed comparator circuit to turn a VGA-level signal into a logic output. I used an AD8561 comparator for this, with an adjustable threshold set somewhere in the middle of the grayscale range.

I also built another one-shot 74LS123 circuit for the vertical sync pulse, because my measurements showed that VSYNC is low for only about 50-60us on most resolutions, compared to the 180us on the SE/30 display. Vertical retrace isn't usually that short so the 74LS123 extends the pulse to a length up to maybe 150us.

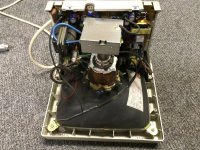

After a bit of surgery on the traces around P4 on the analog board, this was the result driving from VGA resolution on a Quadra 650 (still using the SE/30 logic board HSYNC signal to drive the flyback; I'll look at phase locking later):

Not bad, though not great either. The geometry of the image is pretty good, though even with no delay at all on HSYNC, there is a foldover problem-- the video line starts too soon. The reason for this is that the retrace time on the yoke circuit is too long. It was 4.6us, which depends on the series inductance of the yoke and the width coil (L2), and the value of the flyback capacitor C12, 25nF in this case.

There are two ways to shorten this. One is to make C smaller, which I did, reducing it down to 15nF. The other is to get rid of the width coil which I'd previously measured at about 25% of the inductance of the yoke itself. There's no reason to use the width coil in this circuit anyway, since the supply voltage determines the picture width. (In fact, the later Classic analog boards don't use a variable inductor for width either.)

So replacing L2 with a short circuit and C12 with 15nF, I got this:

Getting there! To get a wider picture I will need a power supply of greater than 20V, and also I'll need to replace the HOT with something that can withstand more voltage. I'm thinking of building a MOSFET circuit like in the Classic analog boards, which will also have the advantage of getting rid of a custom Apple transformer.

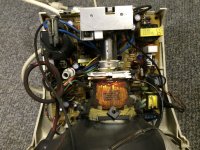

More immediately, though, the video looks a little wonky. There's that bright line on the left side of the screen, which actually only appears when the supply voltage (i.e. width) is large. I'm pretty sure it's some sort of interference between the high-voltage pulse on the yoke and the millivolt-level high-speed comparator circuit. I built all this stuff onto a PCB and everything is bypassed correctly, but there's still a bunch of long wires stringing all over the place from SE/30 to yoke driver to sync/video circuits. Not really ideal for high-speed stuff like this.

Related is the vertical stripes in the video near the left. I'm pretty sure this is also some signal superimposed on the comparator, or a result of running a long single wire from my board to the SE/30 carrying the 25MHz video signal.

The geometry is great though! This really makes me think this can work once it's all properly cleaned up.

]