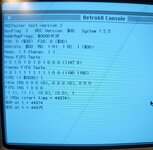

Here are 4 tests with the new app (se/30 ver 3).

Yay, thank you so much! That's more like what I was expecting to see based on your earlier SE/30 test results. Too bad the Ticks variable doesn't give us great timing info, but I think it's enough to provide a decent theory about what's happening.

After pondering some more, I think this is all starting to make sense. Technical stuff that

@Arbee will possibly be interested in:

In the first result, the first IRQ was a "FIFO A and B both half empty" IRQ, even though clearly the FIFOs hadn't filled up yet. My guess/theory: the ASC probably happened to pull out a sample exactly when the FIFOs were just above half empty, causing the half empty condition to be latched into the register even though ASCTester was still filling it up. As soon as I enabled IRQs, it fired immediately due to that. I think it's the same situation I occasionally see on my IIci when there are 2 half-empty IRQs instead of 1.

That one example aside, in general, it looks like what's happening is FIFO A is marked as full first and the IRQ handler is running before FIFO B's sample has been written. This happens repeatedly, and eventually sample B somehow gets written quickly enough too, but it takes a few tries. Then it falls back to expected behavior (a single "half empty" IRQ after I'm done filling it), although I see that we get one more "FIFO A full" IRQ again first.

I think the tests yesterday were going bonkers because I made the ISR too complicated and CPU-intensive by calling Microseconds, and it took long enough that the ASC ate up another sample, so by the time the FIFO B sample was written that should have made it full as well, it wasn't full anymore. In other words my ISR ran for so long after filling FIFO A that it was impossible for FIFO B to ever be full.

The big question: why doesn't this ever happen on my IIci? It's the same ASC chip, right? Maybe it takes a tad bit longer for the IRQ to be signaled on the IIci, so my second sample has already been written before the handler runs? (VIA vs. pseudo-VIA?) Or maybe the IIci's faster CPU is able to write the corresponding FIFO B sample before the IRQ manages to fire. I wonder if I'm supposed to leave IRQs disabled while filling the FIFO or something. I'll have to see what Apple's driver does with the original ASC.

Either way, I think I'm starting to see why they took the "FIFO full" interrupt out of later ASC versions. It's broken (or at least flawed) in stereo mode, at least on the SE/30, because it fires before the B sample has been written. I'm trying to think about how to turn this into an actual test to run.

TBH though, the full interrupt is pointless anyway. It doesn't make sense to use from a software perspective. You wouldn't want to use an IRQ to determine when to stop filling it. You'd poll the status register directly when filling, and then use the half empty interrupt to know when to start filling again.