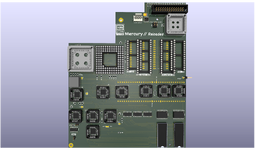

Thanks to the invaluable help of @JC8080 , the schematics for the Mercury 030 RAM board shared by @Bolle have finally been corrected. I've tested them with the RAM ICs (AS4C1M16E5) used in the standalone 4MB RAM board for the 128/512K, and it simply works!Oh crap, I totally forgot about that...

The GALs are available over here on the PLD archive and see the attachment for the schematics if the RAM board.

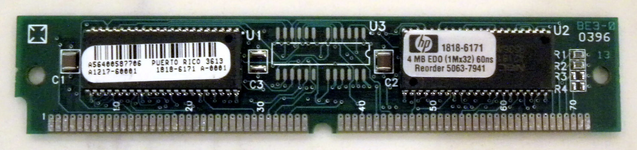

Moreover, it works with the EDO version of these RAM chips. This is a big deal since I haven't been able to find authentic FPM versions (the ones I bought on Amazon turned out to be fake).

JC8080 bought a Mercury board with the RAM expansion a few years ago. Coincidentally, he bought it from the person who posted some nice pictures of it on Reddit. I actually contacted the original owner a few weeks ago, but he told me he had sold it. It turns out the buyer was JC8080!

If anyone would like to make an exact replica of the original RAM board for the Mercury 030 accelerator, or even integrate it into the Performer accelerator board, whether using the original 30-pin SIMMs (80ns or faster for 0 wait state) or these high-density RAM ICs, it can now be done!

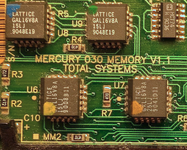

The corrections are as follows:

Pin 4 of RU1A needs to be pulled up, so it should be connected to pin 1 or pin 10. If left floating, it corrupts the output pulse used by the synchronous part of the FSM for RAM refresh.

CLK for RU9 is CLK_30. (CLK_30 and SM_CLK16 are the same signal but are driven separately).

The "Big One": This had me scratching my head for months! Pin 12 of RU9 is actually DSACK1 for 32-bit data transfers, so it is connected to the other DSACK1 output generated on the accelerator board (pin 12 of U4). Checking the equations, it makes perfect sense: these two outputs are never driven by the PLDs at the same time. The DSACK1 from the RAM board only becomes active when the Fast RAM is being accessed; otherwise, it is tri-stated (the same thing happens with DSACK1 from the accelerator board for 16-bit onboard RAM accesses). DSACK0 is generated exactly like DSACK1 from the RAM board, which now seems pretty obvious since both DSACKs must be low for 32-bit word transfers.

That’s it for now!

It is important to add that the only driver that has worked for me (with or without the 32-bit RAM expansion) is the DOVE Racer 030. None of the "Gemstart" drivers out there seem to work in my prototypes. Interestingly, the "External Data Cache" functionality now seems to be activated when selected (the driver icon now shows the word CACHE); I don't know yet if it makes any difference.

Last edited: