Hello Mac community,

I joined MLA68K 2 days ago, because I recently acquired a Macintosh LC475, which I have started to like a lot due to its compact size, and actually very good performance.

Most people know me in the Amiga community, where I have started several hardware designs ranging from sound card, graphics card and cpu accelerators.

So by using Shapeshifter since almost 30 years, one could call me a "passive Mac user", since I have gotten to really like the Mac OS itself, but also the vast choice of native 68k software I could suddenly use on my Amiga at great speed.

I have recently stumbled across the great efforts made by @zigzagjoe to get a 68060 CPU running in a real MAC, something that Amiga users have been doing since a long time, and sadly never passed back to the MAC community due to the emergence of PPC-based machines.

The most prominent headline of this effort, which actually sparked my interest here, was "The Fastest (68k) Macintosh Might Not Be An Amiga Anymore". So I asked myself: well, why not give something back, and make this a reality. Because, at least that's my perspective, what unites both our communities is the love and passion for the Motorola 68k CPU architecture, which, still to this day, is amongst the best, if not the best, CISC ISA ever been created.

(Some people might even claim it should never have been superseded by PPC..... )

)

As a lucky coincidence, I have recently started to make my own Amiga 68060-based accelerator design a while back, which I am waiting now for the very first Revision 0 prototype PCB. Lucky, because I can actually re-use most of my design for a classic m68k MAC accelerator. Therefore, as my introduction to this community, I would proudly like to annouce the:

Prodigy 040/060 Card

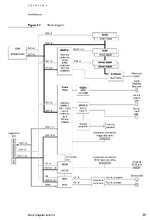

So what is this card? In short, it is a CPU card for classic 68k-based MACs, which plugs directly into the 68040 CPU Socket.

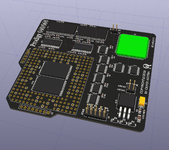

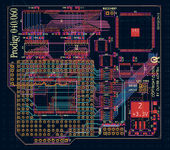

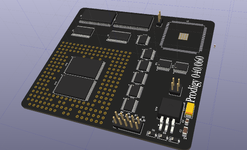

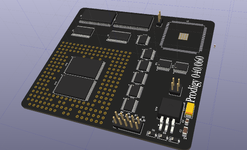

Here is a rendering of the first prototype:

The card will have the following features:

So, what do you think? ;-)

What I would like to ask you is, whether you think this product might be useful to you, and if yes, since I am basically "an Amiga guy", I would appreciate if you could guide me a bit on how these features could be implemented the best way in software to integrate well with MacOS.

So for example, I can design a memory controller very easily, but I have currently no idea how I can make this memory available to MAC OS in the most system friendly way. On Amiga, this is actually quite easy, since the Amiga implements a card resource management system called "Autoconfig", making it very easy to make the OS recognize additional memory and I/O resources (much like PCI).

From what I have gathered so far, the way to go here would be to patch the MacOS Rom to utilize the new resources without getting into conflict with the on-board hardware.

In any case, I shall be looking forward to your feedback and help!

Best regards,

Oliver Achten

I joined MLA68K 2 days ago, because I recently acquired a Macintosh LC475, which I have started to like a lot due to its compact size, and actually very good performance.

Most people know me in the Amiga community, where I have started several hardware designs ranging from sound card, graphics card and cpu accelerators.

So by using Shapeshifter since almost 30 years, one could call me a "passive Mac user", since I have gotten to really like the Mac OS itself, but also the vast choice of native 68k software I could suddenly use on my Amiga at great speed.

I have recently stumbled across the great efforts made by @zigzagjoe to get a 68060 CPU running in a real MAC, something that Amiga users have been doing since a long time, and sadly never passed back to the MAC community due to the emergence of PPC-based machines.

The most prominent headline of this effort, which actually sparked my interest here, was "The Fastest (68k) Macintosh Might Not Be An Amiga Anymore". So I asked myself: well, why not give something back, and make this a reality. Because, at least that's my perspective, what unites both our communities is the love and passion for the Motorola 68k CPU architecture, which, still to this day, is amongst the best, if not the best, CISC ISA ever been created.

(Some people might even claim it should never have been superseded by PPC.....

As a lucky coincidence, I have recently started to make my own Amiga 68060-based accelerator design a while back, which I am waiting now for the very first Revision 0 prototype PCB. Lucky, because I can actually re-use most of my design for a classic m68k MAC accelerator. Therefore, as my introduction to this community, I would proudly like to annouce the:

Prodigy 040/060 Card

So what is this card? In short, it is a CPU card for classic 68k-based MACs, which plugs directly into the 68040 CPU Socket.

Here is a rendering of the first prototype:

The card will have the following features:

- Support for 68040 and 68060 CPUs, selectable by jumper setting.

- CPU clock rate: up to 50MHz (68040) and, yes, 100MHz! (68060)

- SDRAM memory controller, which runs at either 1x or 2x bus speed (to minimize first access penalty) - meaning up to 100MHz memory clock

- 128MB on-board SDRAM

- Flexible bus interface: always full speed to SDRAM, selectable 1/2 or 1/4 bus speed to MAC mainboard (no need to overclock SCSI bus in order to run 100MHz!)

- 2 MB Flash Rom, for startup code, 68060 compatibility software layer and patching of MAC OS

- RECOVERY jumper: if set, system starts using the mainboard ram and rom, enabling you to flash the rom via software

- A prominent Amiga feature: MAPROM - copy the MacOS Rom to superfast SDRAM on start-up, and use memory protection/remapping to execute it as if it were a real ROM - withou the need of using the MMU

- Configuration settings can be flashed in FPGA

- FPGA can be software upgraded on the MAC

- Designed to (hopefully) fit in all 68k-based MACs, first prototype will be developed on an LC475

So, what do you think? ;-)

What I would like to ask you is, whether you think this product might be useful to you, and if yes, since I am basically "an Amiga guy", I would appreciate if you could guide me a bit on how these features could be implemented the best way in software to integrate well with MacOS.

So for example, I can design a memory controller very easily, but I have currently no idea how I can make this memory available to MAC OS in the most system friendly way. On Amiga, this is actually quite easy, since the Amiga implements a card resource management system called "Autoconfig", making it very easy to make the OS recognize additional memory and I/O resources (much like PCI).

From what I have gathered so far, the way to go here would be to patch the MacOS Rom to utilize the new resources without getting into conflict with the on-board hardware.

In any case, I shall be looking forward to your feedback and help!

Best regards,

Oliver Achten

Last edited: