There's already bootloaders et al for NetBSD/Linux from a Mac platform so that piece is already covered if it comes up as a Mac. This way you get the hardware initialization done by the ROM/Toolbox as those kernels don't know how to bring up the hardware from scratch. I just need to get around to adding 060 support from the amiga/mvme targets of netbsd to the mac68k one as it rather sensibly doesn't expect an 060. Shouldn't be complicated, I've just put off getting a build environment set up.

Sounds great, I was also thinking about whether adding MAC as an m68k platform would make sense for Linux Bootloaders such as UBOOT.

Gathering from the MEMC(jr) description and source code, setting up the memory and display shouldnt be complicated.

I was actually thinking of doing this for the low-level bootrom code on all my cards, sharing the same code base. So if you hit a key on both MAC or Amiga, you get the basic monitor on-screen.

Local memory would be much more relevant to the earlier 030 based macintoshes, the IIci and related platforms, for the reasons you mention. It's amusing putting an 040 in these systems, but even a cache can't hide 16 cycle @ 16mhz accesses for a 40+mhz CPU, nevermind slow framebuffers and other IO.

Also, many 030<>040 bus translators can not do bursts / line requests, which additionally hurts performance.

I find myself poking at the 060 ROM stuff from time to time as it's relevant to my interests but in all honesty I can't promise serious continued efforts as I technically reached my goal and there's some very grotty issues remaining for Mac ever supporting 060 fully. I would otherwise be interested in doing some testing but just wished to be fully transparent.

As I said, if you like the challenge of getting Linux/NetBSD running on Mac in a fast 040/060 environment, my card could also be something for you. I'd also love to have a look at NeXT machines, but from where I come, these things are truly unicorns... ;-)

I've been using the ATF15xx series of CPLDs, a superset of the Max7xxx family. Nice capable chips and 5v native, however all code paths are married to the atmel fitter for place and route and it's a tempermental buggy piece of crap. I keep a running list of bugs titled "Reasons to hate the atmel fitter.txt". You can technically develop with altera tools, but then all the added functionality is inacessible and some of that like losing the additional clocks hurts.

It's exactly the reason why I am refraining on using these chips.

Is your FPGA 5V tolerant? Or do you plan to use a 68040V (did they make that in PGA?) for bring up?

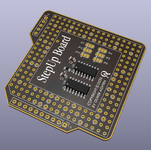

Nope, I'm using the MAX10 series from Altera. They scale well from 2K-50K LE's, and are well suited to be used as glue/logic , memory controller. I have also developed a PCMCIA graphics card using these chips, driving directly an HDMI display at Full HD.

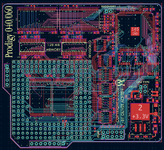

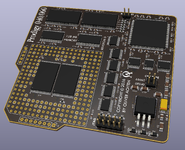

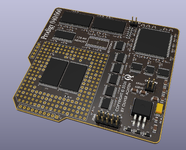

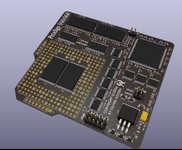

So you can see on the PCB that I have placed quite a lot of bus drivers there, but I think it's okay, in the case of the Prodigy, it's not adding that much complexity or board space. On my A1200 card, which is way more complex, I only support 68060 since I can not fit the bus drivers for the 040 anymore (which is a shame). But I also intend to use the same design for an Amiga 2000 and Amiga 3000/4000 card, where I do have the space again.

Here is a status update (this time Raytraced):

Making very good progress, I think the design will be finished by the end of the week!