Very interesting. Small question here: what is the interrupt or even DMA on a simple memory mapped RAMDisk used for with MacOS ?

All the implementations I know (on 512k/Plus type hardware) were just memory mapped

Generally speaking, interrupt/DMA-based system enables overlap between the CPU and the I/O device, thus are more efficient (and may in some OS enables other features, e.g. reordering of operations via a request queue). In MacOS, a disk driver can acknowledge receiving the request immediately upon sending it to the device, and return control to the OS. When the device finish completing the request,

it is marked as finish by the interrupt handler. I have no idea whether that offers any practical benefit in MacOS 8 vs. synchronous completion (basically, waiting for the I/O to complete before returning control to the OS).

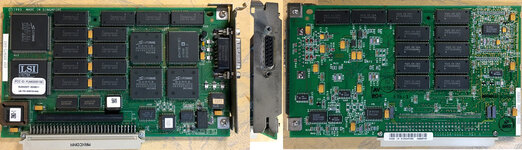

In MacOS, another benefits is that the physical memory space is somewhat limited at 4 GiB. A NuBus device can only map 16 MiB (slot) + 256 MiB (superslot) in 32-bits mode, so a memory-mapped RAM disk is effectively limited to around 256 MiB. The DMA has no such limit, so could expose a much larger device - Artix-7 boards exist with 512 MiB or 1 GiB, but it's possible to go even higher.

For NuBus specifically, the CPU only initiates long word (32-bits) transaction to memory-mapped area, each independent from one another; so a full NuBus cycle is needed for every 32-bits long word, each seeing the full latency of accessing the DDR3 SDRAM. The DMA engine initiates 16-bytes (resp. 32-bytes) pipelined transfers to the memory, and uses 16-bytes (resp. 32-bytes) synchronous NuBus block transfers to/from the memory controller. The data are always transferred in multiple of the sector size (512 bytes), so that's always possible. Overall it's a much more efficient use of the NuBus bandwidth and hide the memory latency better. At least theoretically, because my current implementation isn't faster on the Q650 than trivial memory-mapping using BlockMove :-( (at 16-bytes it's a bit slower, at 32-bytes a bit faster).

Ultimately my primary goal was to debug the DMA/NuBus bus-master bit of the hardware, and test interrupt sharing, rather than improve the RAM disk. Adding a micro-sd card would make a revised NuBusFPGA more useful and would need both features.