Hello all,

Of course it was coming Following the NuBusFPGA and IIsiFPGA, here comes the QuadraFPGA, adding the Highly Desirable Macintosh Interface to Macintosh Quadras.

Following the NuBusFPGA and IIsiFPGA, here comes the QuadraFPGA, adding the Highly Desirable Macintosh Interface to Macintosh Quadras.

It's very similar to the IIsiFPGA, but is designed to connect to the Quadra PDS slot and talk to the 68040 there, including burst support on reads and writes. So far I've only tested it in my Quadra 650. It requires a KEL 8807-140-170LH connector, which are nearly impossible to find: thanks to member @Jockelill for sending me a couple for my prototypes (there's a thread on TD for possible alternate, untested so far).

(there's a thread on TD for possible alternate, untested so far).

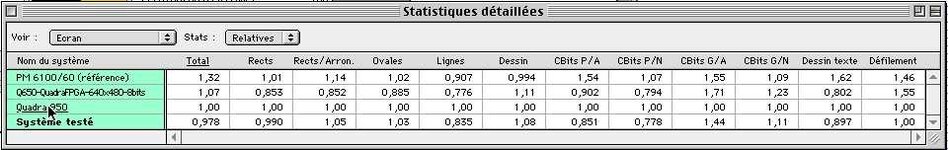

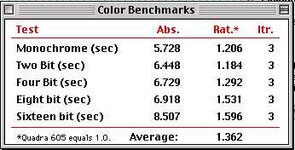

Currently the full Framebuffer available in the NuBusFPGA/IIsIFPGA is supported, including audio & acceleration. It's much faster than either the NuBusFPGA or the IIsiFPGA, thanks to the 68040 performance and the direct bus. Here's some Speedometer 4.0.2 results when set to 640x480 as most other Macs are tested:

Quite happy with that

To limit cost, the board is much smaller than a full PDS card (100mm*100mm, cheap at JLCPCB!), so the HDMI connector is way inside the case; it's not very pretty. A 3D-printed backplate and an extension cable (@Jockelill found that one) would improve things.

Currently it doesn't do memory expansion, as the Q650 I have has no ROM slot, and it seems it will be more complicated than on the IIsi due to the more complex memory controller & associated initialization.

.It's all on GitHub as the others.

Of course it was coming

It's very similar to the IIsiFPGA, but is designed to connect to the Quadra PDS slot and talk to the 68040 there, including burst support on reads and writes. So far I've only tested it in my Quadra 650. It requires a KEL 8807-140-170LH connector, which are nearly impossible to find: thanks to member @Jockelill for sending me a couple for my prototypes

Currently the full Framebuffer available in the NuBusFPGA/IIsIFPGA is supported, including audio & acceleration. It's much faster than either the NuBusFPGA or the IIsiFPGA, thanks to the 68040 performance and the direct bus. Here's some Speedometer 4.0.2 results when set to 640x480 as most other Macs are tested:

Quite happy with that

To limit cost, the board is much smaller than a full PDS card (100mm*100mm, cheap at JLCPCB!), so the HDMI connector is way inside the case; it's not very pretty. A 3D-printed backplate and an extension cable (@Jockelill found that one) would improve things.

Currently it doesn't do memory expansion, as the Q650 I have has no ROM slot, and it seems it will be more complicated than on the IIsi due to the more complex memory controller & associated initialization.

.It's all on GitHub as the others.