Stephen_Usher

Well-known member

I've been handed an LC III which had some localised battery damage but the CPU pins got damaged and the previous owner tried to fit a new CPU, got stuck and handed me the machine.

I've replaced the CPU with another one and although it doesn't look great all the legs tone out correctly.

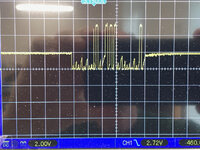

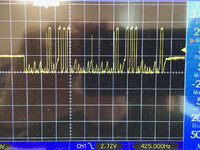

However, the CPU on power up only goes through a small number of read cycles, /BUSERR goes low for about 10ns and the CPU stops with /HALT still high.

Attached is an image of the activity measured using a logic analyser.

I don't have a hex dump of the ROM so I can't see it the top nibble is correct for the first few words. (I was looking here for addresses as the beginning of the ROM reading should be giving the CPU addresses to set up the jump table, interrupt vector, stack and program counter.

Resetting the machine gives the same result.

I've replaced the CPU with another one and although it doesn't look great all the legs tone out correctly.

However, the CPU on power up only goes through a small number of read cycles, /BUSERR goes low for about 10ns and the CPU stops with /HALT still high.

Attached is an image of the activity measured using a logic analyser.

I don't have a hex dump of the ROM so I can't see it the top nibble is correct for the first few words. (I was looking here for addresses as the beginning of the ROM reading should be giving the CPU addresses to set up the jump table, interrupt vector, stack and program counter.

Resetting the machine gives the same result.