Looking to develop some midrange affordable ZIF upgrades. Seems like there might be a market for upgrades in the $100-$200 range. Will probably try to make 533MHz 7410s, and 733MHz 750FX. I mostly just want practice in PCB CAD software. I have been a technician for going on 20 years, doing a lot of surface mount soldering, but unfortunately my last job injured both my thumbs, and holding a soldering iron results in an unfortunate combination of pain and tremors. Hoping to get a job professionally doing CAD. Any PCB I personally design will be thrown up on GitLab as FOSHW.

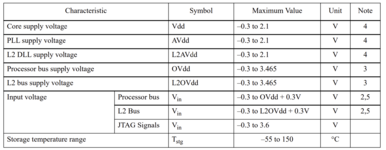

My plan is to make an interposer to adapt 750FX CPUs to replace 750/750L. I also would like to try 750CL. I know the 750FX has an additional PLL jumper, so the interposer would need an extension of some sort for that. If anyone knows any other issues I might encounter, or if there's other CPUs that'd be easy to adapt, I'd appreciate the input.

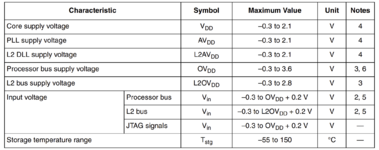

One question I have is if the back-side cache would simply be treated as L3 cache? Or should I just remove the backside cache altogether? Are there any voltage differences or anything else that a simple interposer would not address?

My plan is to make an interposer to adapt 750FX CPUs to replace 750/750L. I also would like to try 750CL. I know the 750FX has an additional PLL jumper, so the interposer would need an extension of some sort for that. If anyone knows any other issues I might encounter, or if there's other CPUs that'd be easy to adapt, I'd appreciate the input.

One question I have is if the back-side cache would simply be treated as L3 cache? Or should I just remove the backside cache altogether? Are there any voltage differences or anything else that a simple interposer would not address?