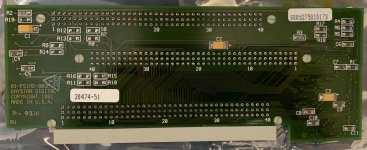

I have a theory... The Artmix adapter is a clone of the adapter that was made for the DiiMo Cache 030.

It looks like that one handles the /STERM signal different than the PowerCache. I will modify one of my adapters and see if the performance rating changes if I run /STERM through the GAL just like on the Artmix adapter or wire it up straight through between the PDS and cache slot on the adapter like Daystar did on the IIsi adapter.

Not sure how they did on their official SE/30 PowerCache adapter as I do not have one of those.

If the performance rating changes you can run a simple wire (or change the code in the GAL)

On the SE/30 DiiMo they are doing this in one of the GALs and I am pretty certain the same is going on in the Artmix/DiiMo SE/30 adapter as well. (at least I did this in my SE/30 adapter and I am getting the same results so I again I am sure this is what Artmix and I am doing)

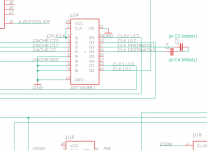

Code:

CPUCLK=1 /STERM.PDS=2 GND=10 /nc11=11 o12=12 f13=13 f14=14 f15=15 CPUCLK.OUT1=16

CPUCLK.OUT2=17 STERM.OUT=18 o19=19 VCC=20

@ues 0000000000000000

@ptd unused

equations

o19 = gnd

o19.oe = gnd

/STERM.OUT = /f13

o18.oe = vcc

/f15 = /STERM.PDS * /f15

+ /STERM.PDS * /CPUCLK

f15.oe = vcc

/f14 = /f15

f14.oe = vcc

/f13 = /f14

f13.oe = vcc

/CPUCLK.OUT2 = /CPUCLK

CPUCLK.OUT2.oe = vcc

/CPUCLK.OUT1 = /CPUCLK

CPUCLK.OUT1.oe = vcc

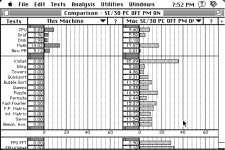

If I get this right this will align /STERM to the 16MHz clock on the PDS interface and then delay it for a few nanoseconds (depending on the propagation delay of the GAL that's used) and finally output that signal to the accelerator.

I can imagine this might throw off the bus/cache logic on the PowerCache if it wasn't designed to wait for that delay.

In the end the SE/30 could be something totally special and require even more magic on the adapter to use the Universal PowerCache to its full potential.

EDIT: changing /STERM to straight through wiring like on the IIsi adapter doesn't do anything to the performance rating. :/