I hope my explanations about prototyping board development have been clear enough. I'm not so good with getting things across in words, that's why I document progress in pictures. I've been told that doing so helps quite a lot in getting my notions across.

At any rate, here's a better attempt at a summary of events in this thread:

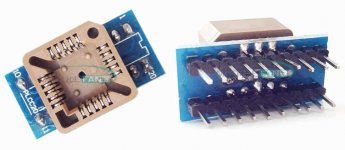

I've been slowly letting go of the notion of wire wrapping the the entire board as I've been ruthlessly applying the KISS principle. I originally wanted to put the GAL prototyping area on the main PCB, but have realized along the way that keeping the main board simple is very important.

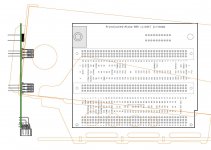

Moving the GAL I have in hand to a daughtercard transfers complexity off the oversize/expensive main board while adding flexibility. Adding a DIP socket “in series” with the SMT GAL socket for. testing reproduction versions was in my original spec for the ProtoCach1 wire wrap board. Minimal costs of making up sets of Rpi oriented SEEED boards (used as generic term) has made utilizing them in the daughtercard role a no brainer to me. Such has allowed me to reduce the size of the main board significantly.

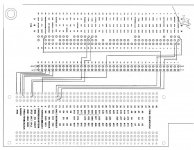

I'd worked out a very labor intensive method for using my VinylCAM PCB process to produce a wire wrap oriented board combining soldered connectors with wire wrap headers. I've also got laser print etch mask here, but have never tried it, so I stuck to the tries and true. I decided moving entirely to wire wrap on perf board might be the KISS way to go, built a partial implementation and started this thread.

Themk's cost analysis of various sizes of SEEED boards made me realize that moving back from full-on wire wrap to etched copper would a significant amount of time and effort. A little help and a little over $100 in trade for sweat equity made perfect sense as that decision was made during tax return season.

I'd originally wanted to implement SMT buffering/line driving components for testing more than the two card limited PDS spec. but that fell by the KISS oriented wayside. Board size/cost tradoff pressures have been squeezing my simplified wire wrap header areas coupled to soldered connectors off the board and back onto wire wrap connectors.

I traded the cost of adding another two layers in order to move as much of the wire wrapping of the control line adaptation circuitry onto copper. Per BMOW's suggestions that meandering in wire wrap won't be necessary for the 16MHz SE/30 testbed, I've begun thinking in terms of implementing the 64 Address/Data lines in copper on the ProtoCache board as well. I was thinking that meandering might rear its ugly head on my 25MHz clocked IIsi board, but I'll cross that bridge if and when, might as well burn it for the time being, permanently with luck.

My drilled out via (pre-positioned/single purpose/almost totally unnecessary adjacent triplets per signal) cut and patch process makes moving adaptation oriented addressing rework to short lengths from my now redundant wire wrap spools a snap. Has anyone else used this method? It's one of my normally crazy ideas, but it's hard to image it hasn't occurred to some other lunatic. Such was unnecessary back in the wire wrap day, but things have changed dramatically, so it makes more sense than ever to me in this SEEED age.

At any rate, we're now looking at ready to go ProtoCacheX board development, fully implemented in copper across four layers. The KISS principle eliminates all wire wrap headers to the daughtercard interface at this point. Additional pins will be added as necessary to those drilled out via cutout locations. Wire wrap is far more flexible than directly soldering patch connections during the experimental period. Desoldering the two pins and restoring their drilled out connection with wire wherever jumpering proves unnecessary jibes with the KISS principle in my book.

Dedicated cut and patch provisions for mix and matching traces to the daughtercard pins should keep connections for the adaptation to the 19 lines available (+5V and GND take up the first two) on a single 2x20 header/RA socket interface. Putting the usual suspects on the first 19 pins KIS. Those extra 18 or 19 thru-holes and related signal cutouts provide a comforting level of insurance.

GAH, I really hate writing! What can I do to further clarify this attempts at summation?

Questions?

edit:

SWEET! [

] ]'>

Here's the link to a similar reboot that does much in explaining the overall project and adaptation development process.

Cloning the Daystar PDS Adapters for the IIsi and SE/30 - Take 2