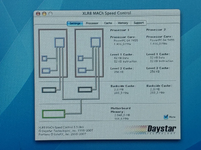

Hi, I've been trying to view the cache speed on my 2x1.42GHz MDD with OS9 and Gauge Pro, but it doesn't show any information about either L2 or L3. I can't find any app that gives me this information.

Is there a version of Gauge Pro for OSX? Or what app could show me the L3 cache speed, or at least the ratio?

I've been told it's in a register called L3CR, but I don't know how to access this register.

Thanks.

Is there a version of Gauge Pro for OSX? Or what app could show me the L3 cache speed, or at least the ratio?

I've been told it's in a register called L3CR, but I don't know how to access this register.

Thanks.