You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Reverse Engineering the Macintosh SE PCB & Custom Chips for 1:1 reproduction

- Thread starter Kai Robinson

- Start date

cheesestraws

Well-known member

I'll look again in daylight; but it definitely isn't 33. I've only got 22 µF in stock, if it's 21 on the boards I'll just whack a 22 in and hope for the best.

cheesestraws

Well-known member

I zoomed on the original photo and it is brown21 it is!

Cheers! @Kai Robinson one more correction for the BOM, I'm afraid...

Phipli

Well-known member

Well, while I'm at it I thought I might as well upload my SE reference photos in case they are any help more generally.

http://stuffandnonsense.elephantandchicken.co.uk/?p=1292

http://stuffandnonsense.elephantandchicken.co.uk/?p=1292

Kai Robinson

Well-known member

Double checked both of mine - they measure 33uH and the colour code matches :/

cheesestraws

Well-known member

Well, hopefully that just means that it isn't too picky about what that value is!

Phipli

Well-known member

What years are the boards? Are they from the Cork factory?Double checked both of mine - they measure 33uH and the colour code matches :/

Kai Robinson

Well-known member

I would imagine any value from 20 to 40uH would be fine - it's used to isolate the rear I/O only.

Kai Robinson

Well-known member

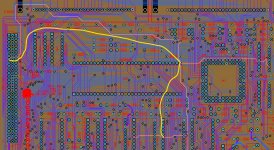

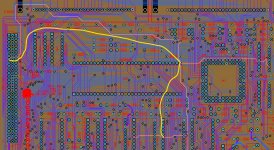

Assembled my Rev 1.4c to bird seed stage, slipped with a pair of tweezers and thought i'd cut some traces - i hadn't, but i DID discover a bodge wire is needed! just the one, thankfully.

Attached is the badly scribbled annotation

I missed one single trace off the back, between two via's - i blame the fact sprint makes everything look like a box of liquorice allsorts, and i was hungry. Or tired. Or both.

Attached is the badly scribbled annotation

I missed one single trace off the back, between two via's - i blame the fact sprint makes everything look like a box of liquorice allsorts, and i was hungry. Or tired. Or both.

cheesestraws

Well-known member

Progress update: all the IC sockets and diodes on now. Electrolytics, crystals, and the big inductors left. I'll take a photo shortly. I've lost the bag of 33µF caps that I bought for this project, which is annoying, so I'll have to get more; not because I need more, but because the only reliable way of getting the first batch to turn up is to order more...

quorten

Well-known member

Missing address line A5, definitely can't boot without that.

So, I dove into seeing how much of the essential functionality of the BBU I could write in Verilog, and I have to say I'm surprised with the progress I've made so far. As I've suspected, most of its features and functions can be implemented with just a whole lot of combinatorial logic, and the sequential logic is almost exclusively simple timers and counters of a sort. I feel that the integrated asynchronous DRAM controller is by far the most complicated part of the BBU, to show how simple the chip is... Here's a sneak peek of my work-in-progress:

bbu.v

It compiles, but I have yet to write a few more missing functions before I start writing the test bench. Hopefully with the existing knowledge we have so far, that mega-oscilloscope @Kai Robinson picked up will mainly be used for confirming signal timing and not so much "black box" reverse engineering.

So, I dove into seeing how much of the essential functionality of the BBU I could write in Verilog, and I have to say I'm surprised with the progress I've made so far. As I've suspected, most of its features and functions can be implemented with just a whole lot of combinatorial logic, and the sequential logic is almost exclusively simple timers and counters of a sort. I feel that the integrated asynchronous DRAM controller is by far the most complicated part of the BBU, to show how simple the chip is... Here's a sneak peek of my work-in-progress:

bbu.v

It compiles, but I have yet to write a few more missing functions before I start writing the test bench. Hopefully with the existing knowledge we have so far, that mega-oscilloscope @Kai Robinson picked up will mainly be used for confirming signal timing and not so much "black box" reverse engineering.

Kai Robinson

Well-known member

Oh, now this is interesting....might be worth reaching out...

http://www.byrdsight.com/apple-macintosh/

http://www.byrdsight.com/apple-macintosh/

Kai Robinson

Well-known member

Also @quorten - you may have already seen this, but might give you some insights with regard to the BBU: http://www.retro.co.za/ccc/mac/ReverseEngineering/PALs.html

quorten

Well-known member

Actually @Kai Robinson that last link was a new one to me, and it answers the question I had about the 3.7MHz clock! Considering the Macintosh Plus does not generate a constant-period 3.686 MHz clock signal, but interleaves 3.133MHz and 3.916MHz periods, it is likely safe to assume the BBU does likewise, rather than using a PLL and precise frequency division to get a more accurate 3.686MHz clock.

The first link I saw earlier. Yeah, Pete Foley has his screenshot of the signals simulator source code, purportedly he's got the full thing hiding out. Hardware design tech has definitely changed a lot since then, though.

The first link I saw earlier. Yeah, Pete Foley has his screenshot of the signals simulator source code, purportedly he's got the full thing hiding out. Hardware design tech has definitely changed a lot since then, though.

Kai Robinson

Well-known member

Kai Robinson

Well-known member

Posting these - these are the unitron PAL reverse engineers of the original 512k Mac - which should still be applicable. Also, found this passage of text - @quorten this'll be of interest to you:

About six months after the Macintosh was introduced, Apple announced two improvements: the external floppy disk and the 512K model (known as the "Fat Mac"). Though this new machine replaced 4164 chips with the 41256, its timing was not changed to take advantage of this. A year later the Mac Plus brought the use of SIMMs for memory expansion and a SCSI interface for external peripherals, but otherwise was still the same design. The next model, the Mac SE, replaced the PALs with a custom chip and represented the first revision to the machine's timing in four years. They used the memory's "page mode" to read the video buffer two words at a time, which reduced the average number of wait states that the 68000 suffered while accessing the RAM. Other than this complex change, the memory timing was unchanged from the original design even though the memory chips now used were the 120 nS 41256 (with a cycle time of only 230 nS).

So...very possible to include a speedup by just using timings that are relevant, not slow-as-balls based on the 4164's!!

About six months after the Macintosh was introduced, Apple announced two improvements: the external floppy disk and the 512K model (known as the "Fat Mac"). Though this new machine replaced 4164 chips with the 41256, its timing was not changed to take advantage of this. A year later the Mac Plus brought the use of SIMMs for memory expansion and a SCSI interface for external peripherals, but otherwise was still the same design. The next model, the Mac SE, replaced the PALs with a custom chip and represented the first revision to the machine's timing in four years. They used the memory's "page mode" to read the video buffer two words at a time, which reduced the average number of wait states that the 68000 suffered while accessing the RAM. Other than this complex change, the memory timing was unchanged from the original design even though the memory chips now used were the 120 nS 41256 (with a cycle time of only 230 nS).

So...very possible to include a speedup by just using timings that are relevant, not slow-as-balls based on the 4164's!!

Kai Robinson

Well-known member

In addition, i've handed the GLU and ADB chips to porchy from jammaarcade as he has a lot of experience reverse engineering - he's been right on it from the get-go, and reported that the initial equations are indeed correct, but looks like pin 18 is tristate and there's some /OE stuff to sort out still...

Kai Robinson

Well-known member

http://www.merlintec.com/download/unitron1.pdf

http://www.merlintec.com/download/unitron2.pdf

For the full size pdf's of those equations.

http://www.merlintec.com/download/unitron2.pdf

For the full size pdf's of those equations.

quorten

Well-known member

Nice @Kai Robinson. I've been taking a deeper reading of Guide to the Macintosh family hardware and it has been quite helpful in answering several questions on the specifics of the BBU, it also mentioned the double-pace video memory fetch. The timing for the DRAM controller to respond to CPU memory requests looks rather tight, but it's doable if you use both edges of the 16MHz clock and slew rate limiting on combinatorial logic outputs. (Of we could simply use an internal 32MHz PLL and registered state transfers.)

Regarding GLU, indeed a second look at the GLU equations I see no problem with the RTXCA equations, it was the syntax highlighting that threw me off on the additional terms.

Like you've previously said, ADB should be super simple to reimplement our own code if necessary, basically Guide to the Macintosh family hardware has functions of it all laid out: it converts binary data two/from variable-pulse-width trains to represent the bits and it periodically polls the last accessed ADB device for data. Like, literally I'm imagining only 20 instructions or so with that 4-bit PIC.

Another idea that came up (probably looking too far ahead), I believe the ASC on the SE/30 can be reasonably implemented using an AVR microcontroller.

EDIT: Now I think I see why there is the funny thing going on with the address multiplexers for RAS/CAS. It is a required modification to use DRAM fast-page mode since RAS and CAS are still logically "swapped" compared to a contiguous memory layout. This swapping of RAS and CAS is used to get DRAM refresh for free when scanning the video framebuffer.

Regarding GLU, indeed a second look at the GLU equations I see no problem with the RTXCA equations, it was the syntax highlighting that threw me off on the additional terms.

Like you've previously said, ADB should be super simple to reimplement our own code if necessary, basically Guide to the Macintosh family hardware has functions of it all laid out: it converts binary data two/from variable-pulse-width trains to represent the bits and it periodically polls the last accessed ADB device for data. Like, literally I'm imagining only 20 instructions or so with that 4-bit PIC.

Another idea that came up (probably looking too far ahead), I believe the ASC on the SE/30 can be reasonably implemented using an AVR microcontroller.

EDIT: Now I think I see why there is the funny thing going on with the address multiplexers for RAS/CAS. It is a required modification to use DRAM fast-page mode since RAS and CAS are still logically "swapped" compared to a contiguous memory layout. This swapping of RAS and CAS is used to get DRAM refresh for free when scanning the video framebuffer.

Last edited by a moderator:

Trash80toHP_Mini

NIGHT STALKER

I haven't been around for a bit so I'm not up on the last several pages and I don't know if they've been referenced. So if you haven't yet, check out the two years earlier Macintosh Family Hardware Reference which covers the transition from the "Classic Macintosh architecture" to the "Macintosh SE architecture" in what ISTR as a bit more in depth. Guide to the Macintosh Family Hardware assumes an understanding of that tome and both assume an understanding of the one year earlier Technical Introduction to the Macintosh Family, which describes the Classic Macintosh architecture. Roadmaps to Mac Docs in thread below:

Link above thanks to vintageapple.org, but I didn't see a .PDF version of MFHR either there or out in the cobwebs in a quick search. I've got it in hard copy, worth every penny.

Link above thanks to vintageapple.org, but I didn't see a .PDF version of MFHR either there or out in the cobwebs in a quick search. I've got it in hard copy, worth every penny.

Last edited by a moderator:

Similar threads

- Replies

- 7

- Views

- 980

- Replies

- 9

- Views

- 2K