Arisotura

Well-known member

I made a quick FPGA emulator thing, so I could confirm my observations before making any attempts. Good thing I did, I'd read some of the check values wrong, and in practice the check values for the horizontal counter are offset to account for propagation delays.

The HBlank values are actually correct, but the HSync values are off by 16 pixels. The VSync values are off by 2 lines, and the VBlank lasts two lines more than normal.

The HSync part would be tricky to fix due to how the circuitry is laid out -- bits 0 and 1 of the horizontal counter are checked together, for either 00 or 11. The required values for HSync start and end would be 0x51 and 0x5D respectively, but they would require changing the circuitry to check bits 0 and 1 separately. The values used are 0x53 and 0x5F -- 16 pixels off to the right. One could go for 0x50 and 0x5C, 'only' 8 pixels off to the left, but I'm not sure if it's worth trying because I don't know how tolerant monitors are.

The vertical counter doesn't exhibit this sort of weirdness, so I was able to fix it by hand-editing the bitstream. I also modified the final HSYNC output to be just HSYNC instead of being XORed with VSYNC, and modified the TLC34075 parameters to disable sync-on-green.

The results of this quick attempt are certainly nice. My Philips monitor picks up the card's picture perfectly, no misalignment, no green tint. My Acer monitor, the picky one, picks up the picture, but it's dim and there's shimmering on the left edge. I guess it doesn't like HSYNC being off, but this is a start -- it used to just completely refuse to pick up the picture and stay in powersaving mode.

I might just call this good enough for now.

-

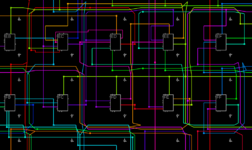

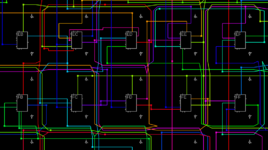

As for the XC3xxx bitstream viewer, I'm close to putting up a first version of it online. I will create a new thread for it I think. Do you folks have any ideas for it? Features you would want to see in it?

The HBlank values are actually correct, but the HSync values are off by 16 pixels. The VSync values are off by 2 lines, and the VBlank lasts two lines more than normal.

The HSync part would be tricky to fix due to how the circuitry is laid out -- bits 0 and 1 of the horizontal counter are checked together, for either 00 or 11. The required values for HSync start and end would be 0x51 and 0x5D respectively, but they would require changing the circuitry to check bits 0 and 1 separately. The values used are 0x53 and 0x5F -- 16 pixels off to the right. One could go for 0x50 and 0x5C, 'only' 8 pixels off to the left, but I'm not sure if it's worth trying because I don't know how tolerant monitors are.

The vertical counter doesn't exhibit this sort of weirdness, so I was able to fix it by hand-editing the bitstream. I also modified the final HSYNC output to be just HSYNC instead of being XORed with VSYNC, and modified the TLC34075 parameters to disable sync-on-green.

The results of this quick attempt are certainly nice. My Philips monitor picks up the card's picture perfectly, no misalignment, no green tint. My Acer monitor, the picky one, picks up the picture, but it's dim and there's shimmering on the left edge. I guess it doesn't like HSYNC being off, but this is a start -- it used to just completely refuse to pick up the picture and stay in powersaving mode.

I might just call this good enough for now.

-

As for the XC3xxx bitstream viewer, I'm close to putting up a first version of it online. I will create a new thread for it I think. Do you folks have any ideas for it? Features you would want to see in it?