nickpunt

Well-known member

"Scientists were so preoccupied with whether they or not they could, they didn't stop to think if they should"

In all seriousness though, has anyone ever attempted to put two accelerators in an SE/30? For example, a socketed powercache and a turbo 68040:

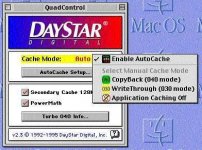

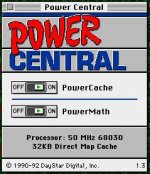

I have no particular desire to be the first to attempt it as I don't want to see two extremely valuable parts go up in smoke, but my understanding is the Turbo040 can be enabled / disabled in software, so if this configuration worked electrically & in drivers, you could have the best of both worlds in software compatibility, given some software works better on 030s than 040s. My guess is daystar software would be rather confused by this whole arrangement, but who knows?

In all seriousness though, has anyone ever attempted to put two accelerators in an SE/30? For example, a socketed powercache and a turbo 68040:

I have no particular desire to be the first to attempt it as I don't want to see two extremely valuable parts go up in smoke, but my understanding is the Turbo040 can be enabled / disabled in software, so if this configuration worked electrically & in drivers, you could have the best of both worlds in software compatibility, given some software works better on 030s than 040s. My guess is daystar software would be rather confused by this whole arrangement, but who knows?