Ladies and gentlemen, my next trick is impossible improbable...

It seems like the IWM is the only (or at least the biggest) thing standing in the way of a Plus or SE made of entirely new parts - and possibly also the biggest problem for those trying to revive an old board. For completeness's sake, I will acknowledge that there are a few projects (pldSCHWIM, Shim-IWM, IWMLess) that approximate a "null" IWM well enough to make a Mac boot... but don't actually emulate its functions. I want to go further. What I have my sights on is something that walks and talks like an IWM as far as the Mac's bus is concerned but, instead of connecting to a real floppy drive or HD20 or a simulacrum thereof, emulates drives within itself - a Floppy Emu with the middleman cut out, if you like. I've been doing some reading about the IWM and the Disk II and I'd like to start a conversation about this, if you guys will indulge me.

I didn't realize this before now, but the IWM is more than just a single-chip Disk II. Each bit in the IWM's "mode register" that is set to 1 enables a feature that the Disk II didn't have - to wit, the ability to run with an 8 MHz clock (instead of a 7 MHz one), the "fast mode" that enables a 2 µs bit cell (instead of a 4 µs one), the asynchronous mode that buffers the shift register, and the optional disabling of the one-second timer. I suppose my main curiosity is, does the Mac just set-and-forget all these bits? That is, can I safely drop the Apple II mode of the IWM? Doing so would make the task quite a bit easier...

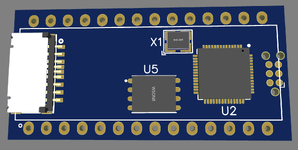

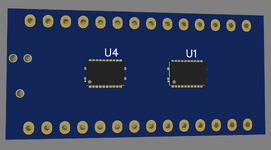

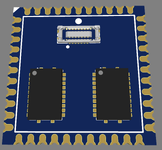

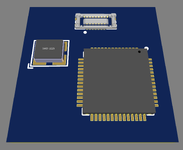

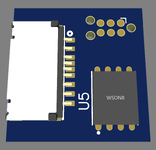

I'm skeptical that it's possible to do this without two chips working in tandem - a microcontroller and a programmable logic device of some kind - so a true drop-in replacement à la the SE's ADB controller is out of reach, but perhaps a PCB module that sits in place of the 28-pin DIP is possible. That and/or integrating a two-chip solution is relatively painless on a wholly remade board such as @max1zzz 's ITXPlus...

Thoughts? =)

Oh, and by the way, if you can afford it, do chip a few bucks to the Internet Archive, it is impossible to overstate how valuable the stuff they've archived is to hackers and hobbyists like us...

It seems like the IWM is the only (or at least the biggest) thing standing in the way of a Plus or SE made of entirely new parts - and possibly also the biggest problem for those trying to revive an old board. For completeness's sake, I will acknowledge that there are a few projects (pldSCHWIM, Shim-IWM, IWMLess) that approximate a "null" IWM well enough to make a Mac boot... but don't actually emulate its functions. I want to go further. What I have my sights on is something that walks and talks like an IWM as far as the Mac's bus is concerned but, instead of connecting to a real floppy drive or HD20 or a simulacrum thereof, emulates drives within itself - a Floppy Emu with the middleman cut out, if you like. I've been doing some reading about the IWM and the Disk II and I'd like to start a conversation about this, if you guys will indulge me.

I didn't realize this before now, but the IWM is more than just a single-chip Disk II. Each bit in the IWM's "mode register" that is set to 1 enables a feature that the Disk II didn't have - to wit, the ability to run with an 8 MHz clock (instead of a 7 MHz one), the "fast mode" that enables a 2 µs bit cell (instead of a 4 µs one), the asynchronous mode that buffers the shift register, and the optional disabling of the one-second timer. I suppose my main curiosity is, does the Mac just set-and-forget all these bits? That is, can I safely drop the Apple II mode of the IWM? Doing so would make the task quite a bit easier...

I'm skeptical that it's possible to do this without two chips working in tandem - a microcontroller and a programmable logic device of some kind - so a true drop-in replacement à la the SE's ADB controller is out of reach, but perhaps a PCB module that sits in place of the 28-pin DIP is possible. That and/or integrating a two-chip solution is relatively painless on a wholly remade board such as @max1zzz 's ITXPlus...

Thoughts? =)

Oh, and by the way, if you can afford it, do chip a few bucks to the Internet Archive, it is impossible to overstate how valuable the stuff they've archived is to hackers and hobbyists like us...

Last edited: