Thanks, the Yin of it is that I tend to "see" connections visually between seemingly unrelated things that more verbal folks don't. The Yang of it is that I have trouble verbalizing what I see so that they'r comprehensible ....

While I'll admit there's moments when it can be a little difficult to follow some of these threads because of their... sometimes scattershot nature, overall I appreciate bait being thrown out there for technical discussions. Even the ones that end up as little more than a trip down a rabbit hole and never produce anything particularly actionable can at least trigger some... non-linear thinking that pays off later.

You quoted me above as having said it was done around 2005 in the second post. That was mistaken, it was probably done more like 2003 or earlier using ribbon cable wired up between SIMMs and jumpers from the mobo soldered up in a horrible fashion, which led dr. bob say something on the order of "That is just evil!"About the only negative thing I'd say here is the opening could have been a little clearer about whether this is a thing that was actually pulled off at some point and was lost to history, or if this was a (potential) cul-de-sac that was vaguely discussed at some point but never went anywhere.

Was looking to post this pic:(And greater specifics about *where* it was discussed would obviously be useful. And, also, for instance, you open with a reference to "that 2012 SIMM recreation thread"... by all means feel free to include links to the supporting material you think are relevant so anyone who might be interested in joining can more easily figure out the backstory?)

(which didn't work yesterday) that I had uploaded to this thread:

I was trying to get a topic posted before work, asking about possible availability of MicroQuadra schematics in the hopes of getting a quick reply. Maybe I should go back to using my "Random Questions thread for such?

Thanks, I think that was what 360Alaska meant as well. It was late, I took it badly, however I did wait until morning to reply.If we could work on the clarity and grounding just a *little* it might make the ideas in the threads more accessible, and therefore actionable? (And thus possibly goosing the completion rate a bit?) Just tossing that out there as a maybe a nice-to-have.

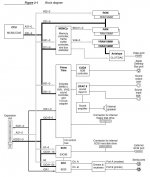

Yep, the RAS lines "address" the columns implemented in memory across banks in the Macs I've looked into. That's why I object to "soldered" standard memory as a mechanism for laming low to midrange Macs. Soldered minimal RAM configs limit the machine to a pittance on just one of two or less than the four available banks of any given controller. I can't imagine Apple spending the money to develop a "Three Bank" memory controller when all they had to do was limit the memory addressing hardware implementations on all but the high end Macs and use the same controller unbridled on the chosen few.Anyway... back on topic, I guess?

Just tossing this out there: do you know for sure it's the RAS lines that are unique between the SIMM socket and the onboard memory? I only ask because I went to my go-to "DRAM memory for Dummies" schematic (IE, the Dynamic Board Commodore PET schematics) and in that case it's the CAS lines that are separate between the two memory banks, RAS are paralleled. I'm scratching my head a little as I read this to try to figure out if it would matter on a 72 pin SIMM which you had in parallel and which were separate, and... okay, this sentence: "Driving RAS without CAS is probably ok too, but the chip will consume its active current (approx 1000 times the idle)" makes me think you're probably right, it's RAS they separate. Maybe that didn't matter with 4116s.

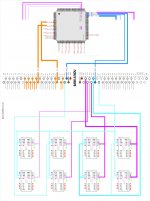

I mean, in principle this seems like a potentially easy hack as long as the ROM in the system can actually grok the idea that there's more than X much memory in the bank allocated to the onboard RAM and the rest of the data/address lines are all wired in parallel between the motherboard socket and the RAM bank. The other thing that maybe be worth mentioning: a 128MB SIMM is a dual-banked; according to the document I linked above when you're using a 72 pin SIMM in a 32 bit configuration each bank uses 2 of the four RAS lines. Since the 605 only has 4MB soldered on the board, which is presumably all one bank, I kind of wonder if ultimately you'd be limited to 192MB, not 256, because the memory controller might not have a fourth set of RAS lines. (IE, the RAM controller only supports 3 total banks, not four.) I have no answer to that in a vacuum.

IIsi with 64MB limit for Bank B and lamed to 1MB in Bank A using the same controller as the 128MB IIci and also SE/30 (with an earlier controller?) would be the prime example.

Memory for the LC was limited to 10MB in ROM as an insurmountable barrier. My God, you might be able to have a competitive memory allocation on a low end Mac!

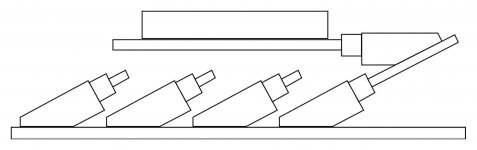

Using a 72-pin SIMMplus™ type card as roughly shown in the pic above might place a pair of 128MB SIMMS above the depopulated memory IC pads parallel to the mobo in the low profile MicroQuadra cases. It's an insane hack, almost nobody would really want to jumper RAS lines from the mobo pads or even worse, unimplemented address lines (used as CAS) AND unimplemented RAS lines from the legs of the memory controller . . . but what the heck?

Maybe I should start this over in a new thread? This one has been well and truly derailed.

I have recently been concentrating on completing just TWO of my many current projects for now, but I'll still be posting my Hack Concept Threads. [

Last edited by a moderator: