Kinda like taking stuff apart to see what's inside before powering up to see if it works? [ ]

]

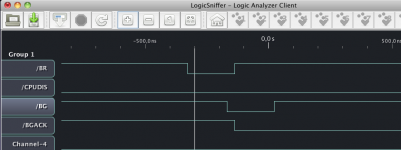

Cool, so it's not multiprocessing, it's flip flopping control of the bus as needed? My scanned info and ill considered WAG was something I doubted after the edit window closed.

Might flip flopping bus control between 68030 MMUMode and 68040 MMUMode to set the system up CPUDIS flip or flop be the reason for those all those calls in the driver?

edit: What's the mechanism within the IIci schematic for CPUDIS synthesization?

p.s. BBCode works much better when you remember the switches. :blink:

Cool, so it's not multiprocessing, it's flip flopping control of the bus as needed? My scanned info and ill considered WAG was something I doubted after the edit window closed.

. . . there's a ton of SwapMMUMode calls in the code...

Might flip flopping bus control between 68030 MMUMode and 68040 MMUMode to set the system up CPUDIS flip or flop be the reason for those all those calls in the driver?

edit: What's the mechanism within the IIci schematic for CPUDIS synthesization?

p.s. BBCode works much better when you remember the switches. :blink:

Last edited by a moderator: