Mustermann

Well-known member

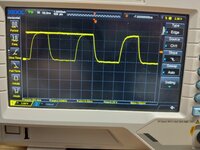

So it would be great to know, how to hack the ROM for this.I should have been more clear, the memory system will run at 40MHz too that way but it will use the timings that are intended for 33MHz operation.

They add more waitstates compared to the 25MHz settings.

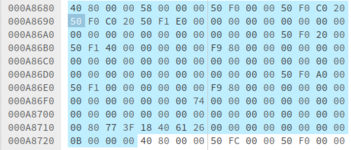

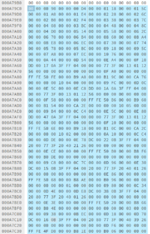

U16 is used to read the state of the configuration resistors onto the data bus. The ROM holds tables for several memory speed configurations and the initialization code sets the appropriate values for each speed configuration.

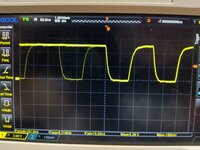

What happens is that you set the 40MHz configuration through the resistors which will tell the clock generator chip to output a 20MHz clock to the CPU clock generator resulting in 40MHz bus and CPU speed.

The problem is that there is no entry in the ROM table for the 40MHz setting hence it fails to post with that setting.

By lifting pin 11 on U16 and connecting it to ground the machine ID will be set to 33MHz and the appropriate memory timings will be used. The memory (both VRAM and RAM) will still be overclocked slightly that way.

If someone of the ROM wizards could modify that table to recognize the 40MHz setting and add the values that we know from the memory controller datasheet no further hardware modification would be necessary.

From my point of view there are two options:

Option1: Find all appropriate tables in ROM and add data for gestalt ID 91/96 (Maybe just copy gestalt ID 90/95)

So with changing the resistors and tables in the ROM, system is expected to work based on Bolle's post above.

Option2: Find the source code for reading the clock settings and change code so data for 40Mhz is the same than 33Mhz.

Someone may know the address where U16 (74F244) can be read.

Based on that the code in the ROM can be found where this address is read and add code.

So Mac ignore that clock pins has changed and operate in 33Mhz mode.

It seems that U16 provide data at D0-D3.

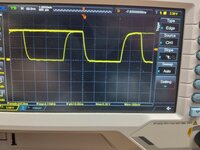

If address is not known, someone owning a logic analyzer may be able to read the address on bus when Gate of U16 is triggered.