Isn't the BlueSCSIv2 already a full featured Pico based SCSI emulator?

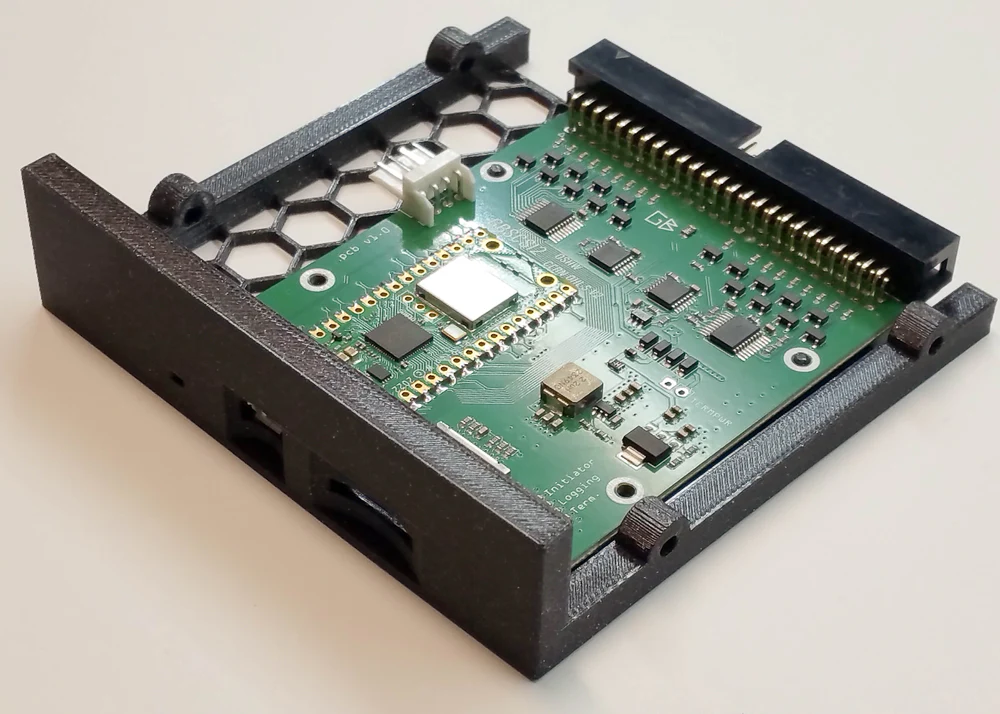

@stormy For what it's worth, GBSCSI

2 is a hardware design that's derived from

ZuluSCSI Pico OSHW board design, which is Open Source Hardware. Rabbit Hole Computing released ZuluSCSI Pico under the CERN Open Hardware License (Strict variant) version 2.0 back in October of last year. GBSCSI2 runs unmodified ZuluSCSI Pico firmware, and I find it frustrating that

@GRudolf94 chose to omit this fact from his original post. Why? It's a doorstop without the ZuluSCSI firmware that enables it to be a functional SCSI-2 emulator. What's the problem with giving credit where credit is due? I have no problem with the existence of GBSCSI2,

at all.

As the person whose business bankrolled the port of

ZuluSCSI to the RP2040 microcontroller (which is the microcontroller used on the original Pi Pico), I feel obliged to correct what seems to be a misunderstanding about the origins of the BlueSCSI Pico

firmware (aka BlueSCSI V2).

BlueSCSI Pico/

V2 was announced (which uses the same exact microcontroller, but without the Pico board, as BlueSCSI V2) was unveiled

ten weeks after the release of ZuluSCSI RP2040.

This is not a coincidence. Nobody associated with BlueSCSI was involved with writing ANY of the firmware development/code that enabled the SCSI emulation to work on the RP2040. The BlueSCSI V2 guys

You don't need to take our word for any of this, since anyone here can see for themselves the commit where the BlueSCSI V2 guys did a mass

search-and-replace of ZuluSCSI with BlueSCSI in their firmware, which was Described as a "rebrand" in the

actual commit in the BlueSCSI repository from November of 2022.

It's important to me that this hobbyist community understands that without ZuluSCSI RP2040, BlueSCSI V2 simply would not exist in its current form. The hardware and firmware development cost tens of thousands of dollars, along with very extensive testing, which I was directly involved with. It's very disheartening to see endless praise being heaped on members of the BlueSCSI team for work they simply appropriated for their own ends.

The ZuluSCSI firmware itself could not exist without the huge amount of effort (and resulting code) which was previously invested in the SCSI2SD command-handling code, which was almost entirely written by Michael McMaster.

On August 12th of 2024, 531 days, nearly a year and a half later, the BlueSCSI V2 project maintainer added the following annotation to the original commit from November of 2022, stating the following:

You were likely given this link as a "gotcha" to prove something bad about BlueSCSI. BlueSCSI has never hidden the fact it was a fork of Zulu. Forks cannot use the someone else's trademarked name, so we of course had to "Rebrand" as this commit says and does.

Zulu was released under the GPLv3 - so

you, I, or anyone were given freedoms to use the code, make modifications, and release our own under a different name - this is how opensource works.

You can see us giving Zulu credit was the first line in our TLDR of the v2 announcement and the 2nd sentence of the announcement part. (

wayback link, Jan 25th, 2023)

While this

is technically correct, nowhere did the BlueSCSI V2 "maintainers" properly credit the actual authors of the work they appropriated. In the open-source world I've been involved with for over 20 years, that's a shitty and deceptive thing to do, and in this case, there was a business case for doing so. The argument from the BlueSCSI guys seems to essentially be "We didn't do anything illegal" which in no way means that their hands are clean. They've engaged in deception from the beginning.

So, again, no one ever hid this fact or never told anyone it wasn't based on Zulu.

This is far from entirely correct. There are

multiple examples of

intentional obfuscations of code merged from the ZuluSCSI code base to the BlueSCSI V2 code base.

For your information here's a few other forks with "Rebrand" commits of prominent opensource forks:

As the first two examples are pure software projects, with no corresponding hardware, I'd argue that this is a

red herring, intended to distract from the real issue, which is that they're commercially

https://github.com/opensearch-proje...f168580ab67ab9b324aeb54f406f9a68e3b6da08c9d0a

This is absolutely correct, and also something we have never hidden in any of our commit history,

unlike the BlueSCSI folks. See

relevant Wayback Machine link here.

- ZuluSCSI was renamed to BlueSCSI v2 (you are here)

The part that's conveniently left out here is that Eric and his distributors sell assembled BlueSCSI V2's, as well as kits, for money. Eric is operating a commercial enterprise, known as

Helgeson Technology Services LLC. That's "running a business" and claiming BlueSCSI V2 is "not a commercial project" when you have authorized resellers globally is

incredibly disingenuous, not to mention delusional.

Despite this fact, a year ago, the BlueSCSI V2 maintainer had the audacity to write the following on Reddit:

"I think mainly the difference is BlueSCSI is not a commercial project, we just give away everything, hardware, designs, etc. We don't pay contractors to write the software, we write it ourselves."

I should note that Eric is seemingly totally okay disrespecting/talking trash about the one contract developer who is responsible for nearly all of the non-SCSI2SD-related code he chose to appropriate. That's rich, folks.

They already had BlueSCSI V1. If it was so great, why did they decide they needed to start completely over with BlueSCSI V2? Maybe it was because ZuluSCSI RP2040 delivered six to eight times the throughput of BlueSCSI V1, blowing it out of the water as a massively improved solution, which cost significant amounts of time and money. It was just too tempting to leave it be.

Finally, I'd like to point out that Eric took it upon himself to administratively block my personal GitHub user account from being able to comment on, file issues related to, or initiate discussions about, anything related to BlueSCSI V2. While he certainly has the right to do this, it's a premeditated and outwardly hostile thing to do. The block has been in place since the BlueSCSI V2 source code repository became public, as far as I'm able to tell. This would seem to speak to his initial intent. I'm still blocked to this day, and I don't expect it to ever change.

github.com

github.com