. . . so I'm not totally crazy

HEH! That'd be

my job description!

)

Haha, I think it fits me pretty well too!

Don't bother putting pads on the backside of the board. As I understand it, the SIMM spec isn't as thick as the standard FRP blanks used by the fab houses. If there's no metal on the backside of the pad area, we can run them over a router bit as I described above, instead of filing away at them the way gamba had to do in order to get the gamba/trag SIMMs to fit.

I agree, but bigmessowires pointed out a very reasonably-priced PCB place that *does* do the correct board thickness. So I may be able to get away with not having to worry about the thickness at all

You might want to move the plated thru holes to the backside far enough away from the front side pads to give a better margin of error for setting up a Router Table/Sliding Table combo.

Are you talking about the vias that are near the SIMM connectors? I should be able to do that pretty easily if we do end up having to use the router.

What's the maximum possible size for an expanded area ROM SIMM for the IIci, SE/30 and IIsi? :?:

If all the lines are hooked up in the pinout that's shown in the wiki, there are 21 address lines that are actually used, for a total of 2^21 = 2*1024*1024 addresses, and each address actually points to four bytes, so that would be 4*2*1024*1024 bytes or 8 megabytes. Is my math right? The SIMM design I'm making hooks up all 19 of the standard PLCC32 address lines, which would allow for a maximum of 2 megabytes of ROM space if we used 4 megabit flash chips.

If anyone has all three machines, a cardboard mock-up that'll clear all obstacles when installed in those three machines would be a good starting point for an in-place programmable EEPROM setup.

True, true! I didn't think about needing it to fit in the SE/30 and IIsi and whatever else there might be!

I guess X-ray wouldn't help too much in this case since the IIsi ROM is also 512k, so it will be different for a 1Mb ROM according to Trag due to the different pin-out.

If the IIsi's ROM is 512 kilobytes in size, that means that it uses four 1 Megabit ROMs for a total of 4 megabits, or 512 kilobytes. Trag was saying that 1 megabit and bigger ROM chips use a different pinout from the 512 kilobit and smaller chips. Since the IIsi does use 1 megabit chips, the IIsi's SIMM should be spot on for the correct pinout

Except it probably won't have some of the higher address lines connected -- I'll check on that, but it shouldn't be too bad to add.

I think having pads on the front and back might be useful for redundancy/reliability in the socket. If the board fab says they can make the proper thickness, then why not just go for the whole package?

As long as Seeed Studio works out, I definitely agree

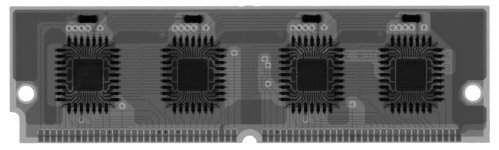

Overall it looks like the placement of components is good. Looks like the caps are moved over for clearance for sockets in case you want to use them? I can't comment on the actual connections. dougg3, did you have a schematic associated with the board or is it based on physical placement alone?

Thanks! Yeah, that's why I moved the caps, to make room for the sockets. I'm definitely not against moving them elsewhere -- even to the back of the board if the need arises. I think they're supposed to be as close to the chip's pins as possible... No, I didn't use a schematic because FreePCB only does the board layout part of things.

I'm probably crazy for not starting from a schematic...