ZaneKaminski

Well-known member

Hi 68kMLA,

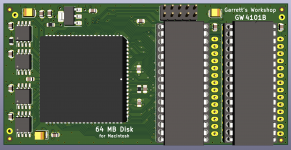

Maybe some people here remember my ARM-based "Maccelerator" proposal from a few years ago. I have cost-reduced the BOM for that project significantly and plan to get the hardware released soon, but that's not for today. Since the Maccelerator proposal, I have been working with a friend of mine, Garrett Fellers, and we have been selling an Apple IIGS memory expansion under the Garrett's Workshop brand. People seem really pleased with that card, so we are trying to get some more of my designs out there. I have a ton of vintage product designs in the backlog which I really wanna release. My post today is about one of them, which we call ROMBUS (or GW4101). It's a 64 MB flash disk interface for Macintosh Plus, replacing its two socketed DIP ROM chips:

The original inspiration for the project was Big Mess O' Wires' Mac ROMinator. When I heard it was being discontinued, I tried to come up with a worthy replacement. ROMBUS implements a 16-bit-wide interface to four SPI flash memory chips. The idea is to get the flash chips into quad read/write mode, in which four bits can be read or written at once from each of four flash memories, thus making a 16-bit interface. ROMBUS interfaces with Mac Plus via the Mac's two ROM sockets. To store a patched toolbox ROM with the flash driver, there are two sockets on ROMBUS which can each accommodate a 512 kilobyte flash ROM, making a total of 1 MB of parallel flash ROM. The Mac Plus has 128 kB of ROM, but can address 256 kB through the sockets, so bank-switching is required to access the total 1 MB capacity. Because the R/W signal is not sent to the ROM socket, writing to the 64 MB serial flash and 1 MB parallel flash is accomplished by bank selection.

I have had boards for this project in hand for 6 months or so, and the CPLD programming is done too, save for any tweaks or bug fixes:

Actually, this is the second revision (GW4101B). The first revision (GW4101A) is basically electrically identical, so the same driver and CPLD programming will work on both, but the flash memory land patterns are wrong, so the GW4201A one can only accommodate 16 MB serial flash despite the board advertising itself as a "32 MB Disk."

I will be releasing the design files for this product soon, under some kind of open-source license, probably GPL, so anyone can make (or sell) their own, or make improvements. We (at Garrett's Workshop) have just finished our SMD assembly line, and we will be selling the card for $40 USD, shipped to the US. Not sure if many will purchase it, since BMOW says his ROMinator was not too popular, but the price strikes me as fair, and I am pleased to have eliminated the need to jumper the R/W signal and the couple of address signals like you have to in order to install the ROMinator. We have 20 of the 64 MB boards, but I want to gauge the interest to see if I oughta order more in preparation for a product launch.

Now, what I need help with is the driver. I have looked at the drivers for the ROMinator and BBraun's previous work, but the way to access the flash memory is different, plus there oughta be a wear-leveling scheme to minimize erase time overhead and maintain the endurance of the flash. (I have a fair solution for the wear-leveling but it takes 256 kB of memory for a 64 MB disk.) My hope is that some other skilled members of the community can assist with the driver development, and then the whole thing can be put onto GitHub for others to build themselves, improve, learn from, etc. And of course we will sell the boards for $40 each, which we think is fair.

So, does anyone want this? Is it fair to ask for assistance on this when we are trying to make some money on sales of the product? And if so, who can assist a little with the driver development? Just pointing me in the right direction in terms of what development tools to use, environment setup, etc. would be really appreciated. Of course, free hardware will be provided to the top contributors. Looking forward to hearing what everyone thinks.

Maybe some people here remember my ARM-based "Maccelerator" proposal from a few years ago. I have cost-reduced the BOM for that project significantly and plan to get the hardware released soon, but that's not for today. Since the Maccelerator proposal, I have been working with a friend of mine, Garrett Fellers, and we have been selling an Apple IIGS memory expansion under the Garrett's Workshop brand. People seem really pleased with that card, so we are trying to get some more of my designs out there. I have a ton of vintage product designs in the backlog which I really wanna release. My post today is about one of them, which we call ROMBUS (or GW4101). It's a 64 MB flash disk interface for Macintosh Plus, replacing its two socketed DIP ROM chips:

The original inspiration for the project was Big Mess O' Wires' Mac ROMinator. When I heard it was being discontinued, I tried to come up with a worthy replacement. ROMBUS implements a 16-bit-wide interface to four SPI flash memory chips. The idea is to get the flash chips into quad read/write mode, in which four bits can be read or written at once from each of four flash memories, thus making a 16-bit interface. ROMBUS interfaces with Mac Plus via the Mac's two ROM sockets. To store a patched toolbox ROM with the flash driver, there are two sockets on ROMBUS which can each accommodate a 512 kilobyte flash ROM, making a total of 1 MB of parallel flash ROM. The Mac Plus has 128 kB of ROM, but can address 256 kB through the sockets, so bank-switching is required to access the total 1 MB capacity. Because the R/W signal is not sent to the ROM socket, writing to the 64 MB serial flash and 1 MB parallel flash is accomplished by bank selection.

I have had boards for this project in hand for 6 months or so, and the CPLD programming is done too, save for any tweaks or bug fixes:

Actually, this is the second revision (GW4101B). The first revision (GW4101A) is basically electrically identical, so the same driver and CPLD programming will work on both, but the flash memory land patterns are wrong, so the GW4201A one can only accommodate 16 MB serial flash despite the board advertising itself as a "32 MB Disk."

I will be releasing the design files for this product soon, under some kind of open-source license, probably GPL, so anyone can make (or sell) their own, or make improvements. We (at Garrett's Workshop) have just finished our SMD assembly line, and we will be selling the card for $40 USD, shipped to the US. Not sure if many will purchase it, since BMOW says his ROMinator was not too popular, but the price strikes me as fair, and I am pleased to have eliminated the need to jumper the R/W signal and the couple of address signals like you have to in order to install the ROMinator. We have 20 of the 64 MB boards, but I want to gauge the interest to see if I oughta order more in preparation for a product launch.

Now, what I need help with is the driver. I have looked at the drivers for the ROMinator and BBraun's previous work, but the way to access the flash memory is different, plus there oughta be a wear-leveling scheme to minimize erase time overhead and maintain the endurance of the flash. (I have a fair solution for the wear-leveling but it takes 256 kB of memory for a 64 MB disk.) My hope is that some other skilled members of the community can assist with the driver development, and then the whole thing can be put onto GitHub for others to build themselves, improve, learn from, etc. And of course we will sell the boards for $40 each, which we think is fair.

So, does anyone want this? Is it fair to ask for assistance on this when we are trying to make some money on sales of the product? And if so, who can assist a little with the driver development? Just pointing me in the right direction in terms of what development tools to use, environment setup, etc. would be really appreciated. Of course, free hardware will be provided to the top contributors. Looking forward to hearing what everyone thinks.

Last edited by a moderator: