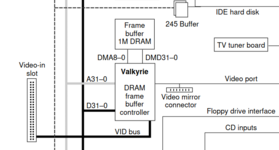

VRAM on performa 5200 is DRAM, 60ns, 1mb, on a 32 bit bus.

I get about 21.8MB/s when I write 320x240x2 bytes (takes about 0.5M cycles, 0.5M/75 MHZ = 0.0067 => 320*240*2/0.0067/1024/102)

(this is with ideal scenario of unrolled 64-bit writes of constant data).

Two estimates for how much vram is being read for the display (640x480 8bpp, 60hz + one video buffer of 320x240 16bpp, scaled):

- 58.6MB/s: (640*480 + 320*240*2*2)*60/1024/1024 - where it would read the video buffer on next scanline again hence x2, as @snail hypothesized

- 43.9MB/s: (640*480 + 320*240*2)*60/1024/1024 - where *if* Valkyrie has a cache for last video line read, it does not need to read from vram

Hypothetically, could get:

- 66.7MB/s: 60ns, 32bit: 1/60ns*32bit/8

- 106.7MB/s: with FPM, assume 1 initial and 3 fast at 30ns. That it has FPM is probably most likely.

Three cases it seems:

1. I get 80MB/s (no cached video line) and theoretical max is about 107MB/s

2. I get 65MB/s (cached video line) and theoretical max is 107MB/s

3. I get 65MB/s (cached video line) and theoretical max is 67MB/s

Does this seem about right? I suppose there is not much one can do to improve on this?

I get about 21.8MB/s when I write 320x240x2 bytes (takes about 0.5M cycles, 0.5M/75 MHZ = 0.0067 => 320*240*2/0.0067/1024/102)

(this is with ideal scenario of unrolled 64-bit writes of constant data).

Two estimates for how much vram is being read for the display (640x480 8bpp, 60hz + one video buffer of 320x240 16bpp, scaled):

- 58.6MB/s: (640*480 + 320*240*2*2)*60/1024/1024 - where it would read the video buffer on next scanline again hence x2, as @snail hypothesized

- 43.9MB/s: (640*480 + 320*240*2)*60/1024/1024 - where *if* Valkyrie has a cache for last video line read, it does not need to read from vram

Hypothetically, could get:

- 66.7MB/s: 60ns, 32bit: 1/60ns*32bit/8

- 106.7MB/s: with FPM, assume 1 initial and 3 fast at 30ns. That it has FPM is probably most likely.

Three cases it seems:

1. I get 80MB/s (no cached video line) and theoretical max is about 107MB/s

2. I get 65MB/s (cached video line) and theoretical max is 107MB/s

3. I get 65MB/s (cached video line) and theoretical max is 67MB/s

Does this seem about right? I suppose there is not much one can do to improve on this?