When all you have is a great big bag of hammers . . .

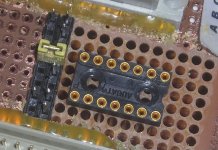

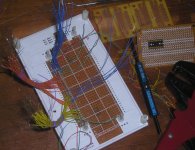

All connections have been unwrapped, clipped to length and stripped. Errant graffiti cleaned off the board and it's ready to go for round two . . . AFTER I finish the homework. :

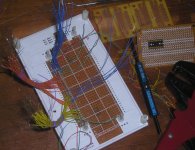

Tried to use the cheapo stripper on the right and went back to the one on the wrap tool after borking a couple of wires. They've been replaced and I'm looking at how best to use a section of the Perf/PCB with the socket on it as a daughtercard for the inverter setup.

All connections have been unwrapped, clipped to length and stripped. Errant graffiti cleaned off the board and it's ready to go for round two . . . AFTER I finish the homework. :

Tried to use the cheapo stripper on the right and went back to the one on the wrap tool after borking a couple of wires. They've been replaced and I'm looking at how best to use a section of the Perf/PCB with the socket on it as a daughtercard for the inverter setup.