I decided to spin this off from my other thread. There seems to be some interest in this, so i decided to move on with the project.

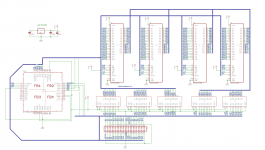

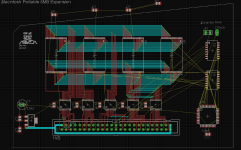

Here is my progress so far:

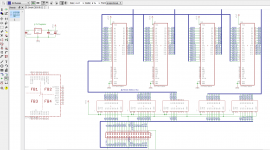

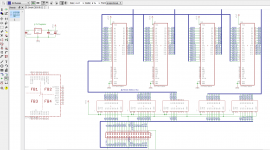

Still alot to go, but so far so good. Got the busses done, just need to get all the signal/enable/CPLD lines ran.

Turns out the apple guide to the family hardware is the correct one. the developer note is incorrect in pin numbering on the socket but the number to signal table figure appears right, and the designing cards and drivers for macintosh is completely wrong. pins and all.

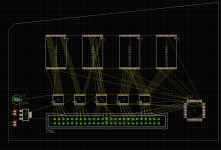

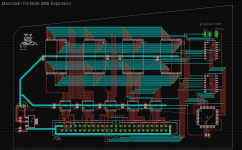

Here is my progress so far:

Still alot to go, but so far so good. Got the busses done, just need to get all the signal/enable/CPLD lines ran.

Turns out the apple guide to the family hardware is the correct one. the developer note is incorrect in pin numbering on the socket but the number to signal table figure appears right, and the designing cards and drivers for macintosh is completely wrong. pins and all.

Last edited by a moderator: