Trash80toHP_Mini

NIGHT STALKER

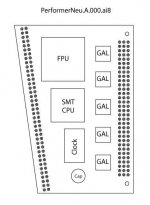

OK, here we go, it's enough to start comparisons withBolle's board and for me to finish degubbing/verification. I hope this helps somebody visualize what's going on within the GALS of my card. To me this isn't gibberish, it's a snapshot album of the functional blocks in my visual schematic:

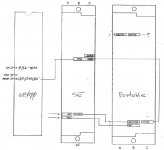

This is what I've got so far with color key.

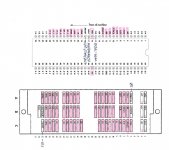

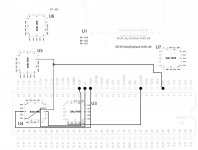

This is the GAL Maelstrom, all the signals I've found so far that pretty much stay within the GALS

These are the only address line's I've found so far that are monitored by the pins of Gals on their way to the 68030

Likewise these are the only control line's I've found so far that are monitored by the pins of GALs on their way to the 68030

This is where it gets really interesting, these control lines are sucked into the whirlpool to emerge or not at is whim, in whatever form.

I have to nail down what's going on with /RW, found an exit (error?) but no entry point. /AS emerges with a large logical disconnect across several GALS. The 16MHz Clock for the 68030 is the major thorn in my side, we'll see.

What's really cool would be the three signals for the 68030 that the GALs synthesize from 68000 signals, where they missing entirely from the 68000 bus.

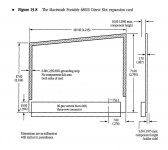

This is a shorthand version of everything that hits the 68030 in the Delta Schematic. The four address lines were stubbed out and labeled at the source, seeing them wend their way through the legs of the GALS was distracting.

Other than what I find by the time I'm through with the rest of U5 and done tangling with U7 and that [&*()&$#] 25MHx Crystal Can, we can pretty much assume everything else is connected 1:1 from 68000 to 68030. We'll see.

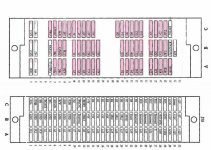

Speaking of crazy timings, here's what I've got so far.

Lemme know if this stuff is helpful or not, I've had feedback both ways in the past and I'm curious how about how the heads of others put things together/take 'em apart. This way works for me. Lets see if it works better in a series of diagrams out of Eagle broken down by function in the layers of Illustrator or the like. [ ]

]

This is what I've got so far with color key.

This is the GAL Maelstrom, all the signals I've found so far that pretty much stay within the GALS

These are the only address line's I've found so far that are monitored by the pins of Gals on their way to the 68030

Likewise these are the only control line's I've found so far that are monitored by the pins of GALs on their way to the 68030

This is where it gets really interesting, these control lines are sucked into the whirlpool to emerge or not at is whim, in whatever form.

I have to nail down what's going on with /RW, found an exit (error?) but no entry point. /AS emerges with a large logical disconnect across several GALS. The 16MHz Clock for the 68030 is the major thorn in my side, we'll see.

What's really cool would be the three signals for the 68030 that the GALs synthesize from 68000 signals, where they missing entirely from the 68000 bus.

This is a shorthand version of everything that hits the 68030 in the Delta Schematic. The four address lines were stubbed out and labeled at the source, seeing them wend their way through the legs of the GALS was distracting.

Other than what I find by the time I'm through with the rest of U5 and done tangling with U7 and that [&*()&$#] 25MHx Crystal Can, we can pretty much assume everything else is connected 1:1 from 68000 to 68030. We'll see.

Speaking of crazy timings, here's what I've got so far.

Lemme know if this stuff is helpful or not, I've had feedback both ways in the past and I'm curious how about how the heads of others put things together/take 'em apart. This way works for me. Lets see if it works better in a series of diagrams out of Eagle broken down by function in the layers of Illustrator or the like. [

Last edited by a moderator: