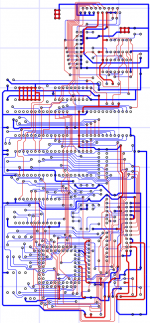

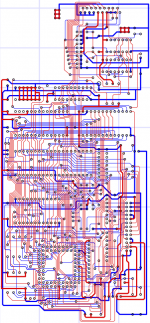

Poor HD-20. I assume the ultimate goal is to lay this out into a 2D schematic? (With the IC's labelled and pin 1 marked?)

Completely off-topic, I happened to stumble upon a vintage computer mailing list post that mentioned in passing how the original Apple Profile drives worked: The short version is that conceptually the Profile drives were very similar to the Disk ][ drives, in that instead of buying "complete" drives from the manufacturer and using their specifications for the digital electronics Apple just bought bare mechanisms and "rolled their own" interface starting from analog up. (In the Profile's case said mechanisms were Seagate ST-506s and 412s.) Anyway, the post mentioned that there is a fair amount of documentation regarding the Profile drive on Bitsavers.org. Look here:

http://bitsavers.org/pdf/apple/disk/

The "Profile Level II Service Manual" goes into gruesome detail about how the Profile drive works, but... here are the bits that are interesting:

1: The Profile digital board used a Z8 CPU to implement the "high-level command set". That's an interesting coincidence, given the Z8 is also used in the HD-20 controller. And:

2: The names of the signals present on the connector between the Profile's digital and "Analog" boards almost exactly match the signals that are named on the patent document describing the Rodime 552 drive. Like... spookily the same. Reading the theory sections makes it sound as if the "division of labor" between the two boards is the essentially the same; In both systems there is a low-level MFM or RLL encoder on the "drive board" (MFM in the case of the Profile Analog board, RLL on the Rodime's board) that accepts serialized data from the "controller board" (via "READ DATA" and "WRITE DATA" lines for "/NRZ serial data"), both have "sys clock" lines (10Mhz for the Profile, 15Mhz for the Rodime, which makes sense for MFM vs. RLL")...

There are differences: In a spooky parallel to the difference between a Disk ][ floppy drive and a Macintosh floppy drive it *appears* to me that the Profile interface breaks out the raw stepper motor connections to the analog/digital interface, while the Rodime, with its own onboard Z8, accepts high-level commands for head positioning. (It says so much in the patent document.) But other than that I'd say with 90%+ confidence that the Rodime drive, for all its "specialness", is in fact just a slightly evolved version of the Profile (At least the mechanism+analog board portion of the Profile.).

As noted, there's substantial documentation for the Profile on Bitsavers; the parallel host protocol is well documented enough that

More than one re-creation

of it exists. The firmware files for the Profile's Z8 are on Bitsavers; it might be *very interesting* to dive into them and see if there are any matching blocks of code compared to the HD20's ROM dump. (Unfortunately there may *not* be that much similarity because of the differing head positioning protocols, but it still might be worth a look if you're really interested in the "Rodime" side of the code.) Complications with the IWM in place of the parallel interface aside I wonder if they might even use the same command set on the host side. (That's a Hail Mary, but you can always hope. The idea there would be is there's some jump table that vaguely matches between the two.) In any case, *somewhere* in the code is the command parser; if you can find it and can work backwards from that point to how it *receives* the command (IE, what torturous things happen between a byte erupting from the IWM's I/O port to that byte making sense to the command parser) you'll almost be at the goal posts.

Oh... Re: "Important discovery":

I would bet you a shiny new nickel that the biggest job that mystery chip does is serializing and deserializing data from/to a buffer in the RAM chip. (This job was mostly discrete hardware on the Profile, which means that chip is probably at least in part a single-chip condensation of the Profile's digital board.) Data will be spewing back and forth from the Rodime at 15Mhz and there's no way the Z8's going to handle that in software. The mystery chip undoubtedly has to put the Z8 on hold and use DMA to cram that data in and out of the RAM at warp speed. Meanwhile, the pins which are connected exclusively to the Z8 are almost certainly the control lines.

The patent doc has some signal names and partial schematics; it's *totally* unclear to me looking at any given partial schematic what the "P" numbers that show signals running off the page refer to. (It almost seems as if the schematics were intentionally partially obfuscated.) Does the (Rodime) board have any labels like "P1" next to its host connector? If it does, you could try matching those pins up to the the schematic fragments and see if, for instance, the serial read/write lines are indeed among those connected solely to Mr. Big Chip.

(EDIT: Profile Level II Service Manual, page 3.36. There's a block diagram. The top 1/3rd and right 1/2 of the diagram, including the shift registers, CRC generator, and Data MUXs... that's probably what's inside that big chip.)