pgreenland

Well-known member

Solved!

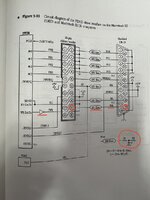

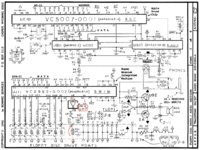

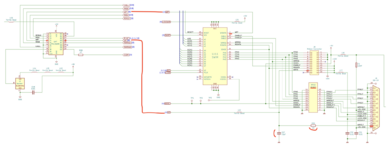

I took a step back over Christmas and had a nose around the schematic again, looking for places where logic between the RAM and the floppy disk meets.

One of the PALs, UH7, manages the write signals to the RAM banks. As well as inverting the write signal from the floppy controller. The write signal that goes off to the drive that is, meaning it's only active during a disk write.

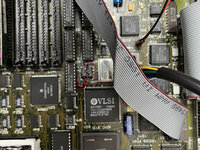

Dropping the logic analyser on the legs of the chip all looked normal and at the same time the problem was gone.

Removing the logic analyser, the problem was back.

Took the chip off, cleaned up the pads, gave everything a good IPA bath and resoldered.

10 floppies written without an error and booting from floppy is now a thing again.

Thanks for the input over the last few months everyone.....it can finally go back in its case at last

Two recapped and fully operational again....two to go

I took a step back over Christmas and had a nose around the schematic again, looking for places where logic between the RAM and the floppy disk meets.

One of the PALs, UH7, manages the write signals to the RAM banks. As well as inverting the write signal from the floppy controller. The write signal that goes off to the drive that is, meaning it's only active during a disk write.

Dropping the logic analyser on the legs of the chip all looked normal and at the same time the problem was gone.

Removing the logic analyser, the problem was back.

Took the chip off, cleaned up the pads, gave everything a good IPA bath and resoldered.

10 floppies written without an error and booting from floppy is now a thing again.

Thanks for the input over the last few months everyone.....it can finally go back in its case at last

Two recapped and fully operational again....two to go