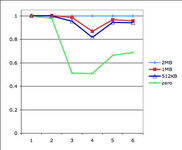

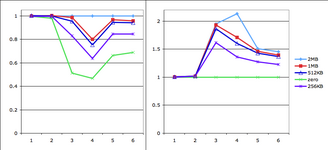

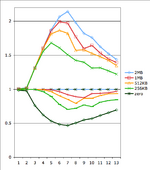

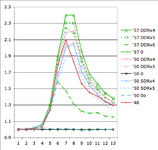

On the G4 CPU, the external memory cache is configured with a register. In the following example a 600MHz 7400 CPU has an actual 2MB of L2 "backside" cache physically existing in hardware, but reduced amounts of 1MB, 512K, and zero L2 cache can also be set in software. This picture is showing a plot of the speed vs data size output from Cache Basher for different settings. The high speed spike at the smallest size is the full speed L1 cache inside the CPU chip, and the slow/flat speed for accessing larger size data is the main RAM at 100MHz on the front side bus (FSB). The jaggy stuff in-between is the L2 backside SRAM cache chips that are external to the CPU but on their own dedicated bus, and of intermediate speed compared to the CPU and main RAM.

So the question is, what types of software can benefit from the external cache? Most simple loops or artificial benchmarks don't show any benefit from larger L2 cache because they fit entirely in a smaller cache. In the Cache Basher plot, I would guess that the jaggy shape of the line is a result of the preemptive multitasking nature of OS X, which is doing a variety of things at the same time by breaking up the CPU time allotted to each activity. I suppose trying two different benchmarks at the same time might show a benefit from larger cache?

While I have this set up for testing, does anyone have ideas on software configurations that might be interesting to try?

So the question is, what types of software can benefit from the external cache? Most simple loops or artificial benchmarks don't show any benefit from larger L2 cache because they fit entirely in a smaller cache. In the Cache Basher plot, I would guess that the jaggy shape of the line is a result of the preemptive multitasking nature of OS X, which is doing a variety of things at the same time by breaking up the CPU time allotted to each activity. I suppose trying two different benchmarks at the same time might show a benefit from larger cache?

While I have this set up for testing, does anyone have ideas on software configurations that might be interesting to try?