I think I got to the bottom of the U7 mystery. The original file

@Bolle dumped has bit 2124 set, which is the AC1 bit for Macrocell associated with Pin 15. This signal is /DS.LOCAL. U7 doesn't actually have any code to do anything with this output. So my assumption is with this bit set and the others unprogrammed, the output ends up always tristated with no signals selected in its matrix. JED2EQN doesn't know what to do with this, doesn't generate anything for it, and when running EQN2JED on the output from JED2EQN, the pin ends up as an output (not-tristated).

This is easy to fix by either adding some code to turn it into a feedback, just turning it to a NC in the schematic, or just using the original dump.

Still fiddling around with the overall logic. I think trying to fully understand it is probably going to just give me a headache, but it is pretty straightforward to do some permutations to make it easier and give some info for sizing purposes. I've attached a file with all equations compiled in a file and the assorted chaff from the decompile process cleaned up. Not an actual file that can be loaded on something, but a easier to work through the logic since it's not split across 12 files.

Analysis gives the following stats (detail attached). The logic needs a bit of further cleanup like guaranteeing uniqueness of outputs (I_HALT_LOCAL was possibly driven by two different GALs) but this is useful for sizing CPLD/FPGAs.

input only (40)

Feedbacks (50) - used both internally and externally

internal feedbacks (13) - only used internally

Output only (11) - only used externally

OEs in use (11) - requires tristate support

registered outputs/feedback (39)

combintorial outputs/feedback (34)

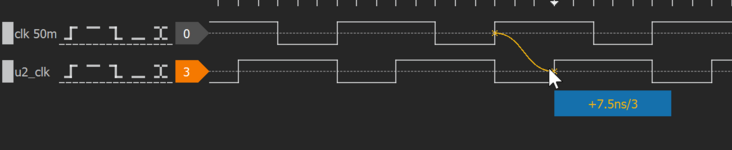

Some of these outputs - the 3 phase shift/invert clocks, and /STERM_PDS - should probably be left in a GAL for simplicity's sake since they exploit the propagation delays of GALs. The rest I don't think are as tightly timed (or use registered, if they are) and I'd think a propogation delay in the 7-10ns window would be just fine. Bigger question would be if CPLD/FPGA could support groups of registered outputs with different clock signals, and tristates... I think so, but I've only ever worked with GALs.

An interesting tidbit, the logic watches for access to SCC, SWIM, or Sound addresses with signal N__11 and then.... does something scary with that in U4. I'm assuming it's slowing things down, somehow, for compatibility, but it touches many of the state machine signals so hard to say quickly.